# **查**香山处理器后端流水线的设计与实现

蔺嘉炜 徐易难 张紫飞 王华强 中科院计算所 2021年6月25日

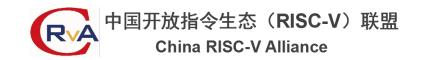

# ⇔香山核后端流水线

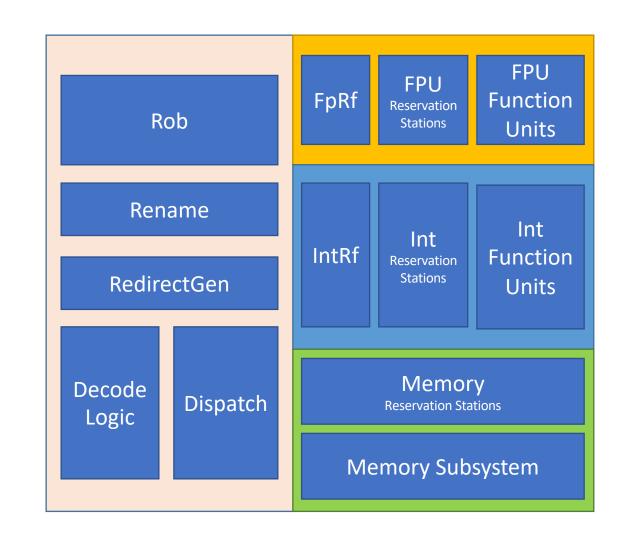

- CtrlBlock

- 译码/重命名/分派宽度=6

- 发射前读寄存器堆

- IntBlock

- 160项物理寄存器

- 4\*ALU + 2\*MUL/DIV + 1\*CSR/JMP

- FloatBlock

- 160项物理寄存器

- 4\*FMAC + 2\*FMISC

- MemBlock

- 2\*LOAD + 2\*STORE

# 拳 香山核后端流水线: CtrlBlock

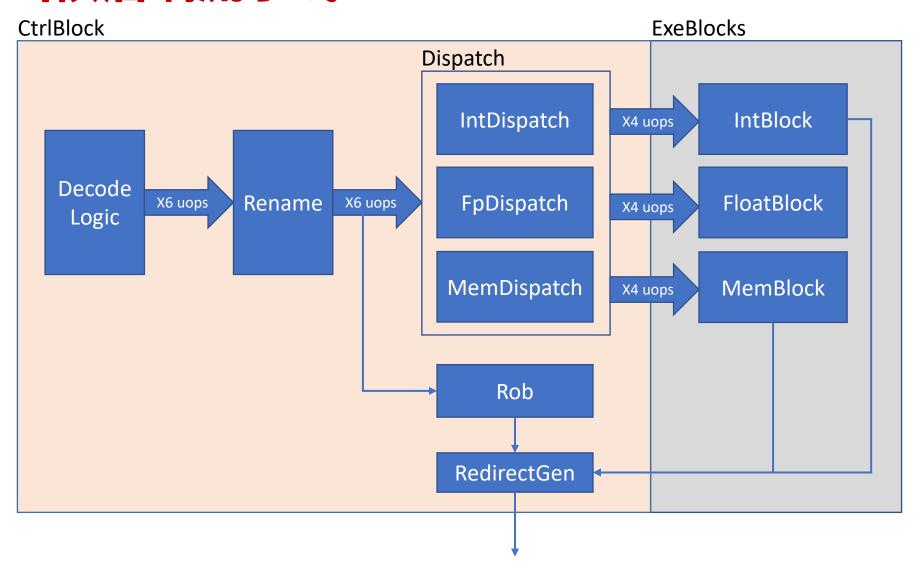

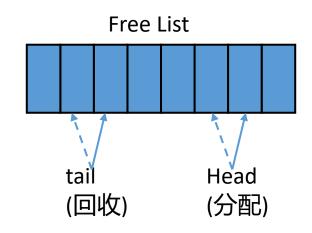

# ⇔ 香山核后端流水线: 寄存器重命名

- 统一物理寄存器重命名

- 32个逻辑寄存器映射到160个物理寄存器

- 每拍可分配/释放6个物理寄存器

- 使用回滚进行恢复

- •回滚时正确路径上的指令可以正常写回

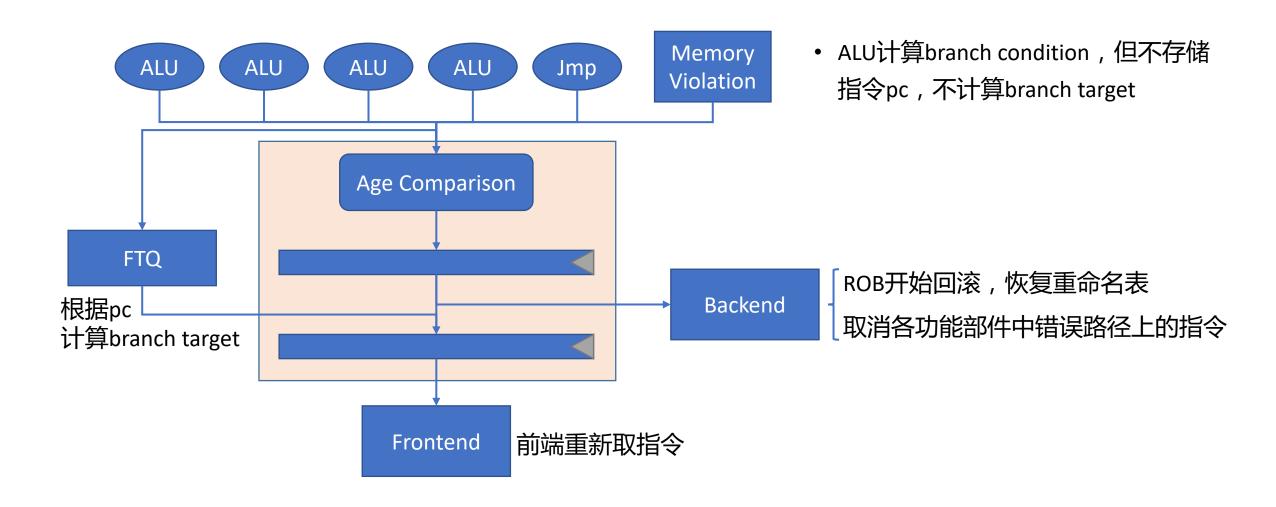

#### ⇔ 香山核后端流水线: 流水线重定向

#### **拳 香山核后端流水线: IntBlock**

- 7个定点保留站,每个16项

- ALU部件可提前唤醒其他保留站,实现背靠背执行

- MUL: 3级流水线华莱士树乘 法器

• DIV: SRT4整数除法器

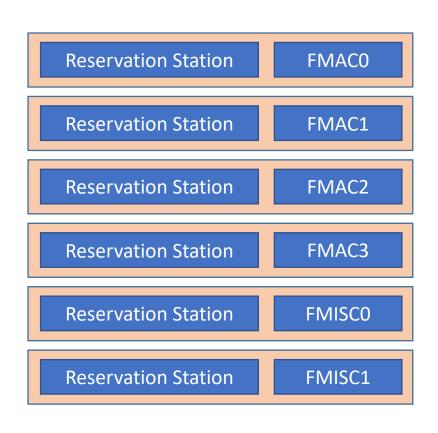

#### **拳 香山核后端流水线: FloatBlock**

- FPR内部采用recode<sup>[1]</sup>格式存储 浮点数(65-bit)

- 浮点功能单元基于Hardfloat实现,对FMAC部件和除法开方部件进行了优化

- 4个FMAC部件,每个FMAC部件 内部4拍延迟

- 2个除法开方部件,均采用SRT4 算法实现

160x65-bit (recode format)

**FPR**

[1]https://github.com/ucb-bar/berkeley-hardfloat.git

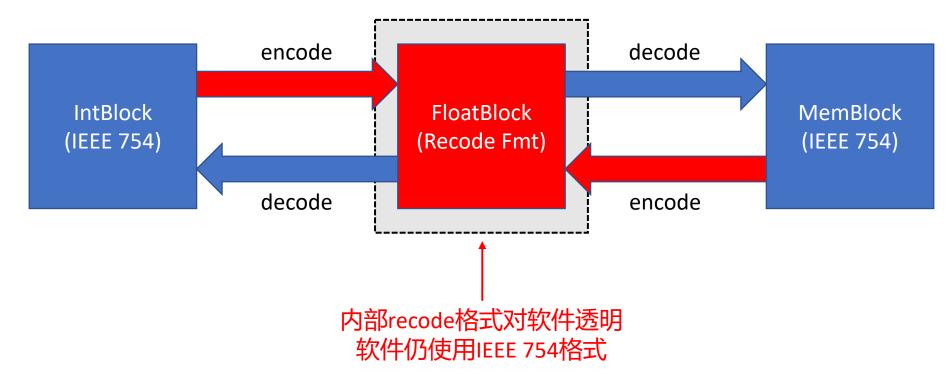

#### **拳 香山核后端流水线: FloatBlock**

- Recode格式: 将浮点数的指数扩展1位,从而使Subnormal能够以

- 1.xxx\*2^exp的形式表示,简化了浮点部件的运算和舍入逻辑

#### **拳 香山核后端流水线: FloatBlock**

- Recode格式的优势

- 简化了浮点功能部件的设计

- Recode存在的问题

- 与定点、访存交互时的格式转换带来了额外的延迟

- 对实现向量扩展不友好

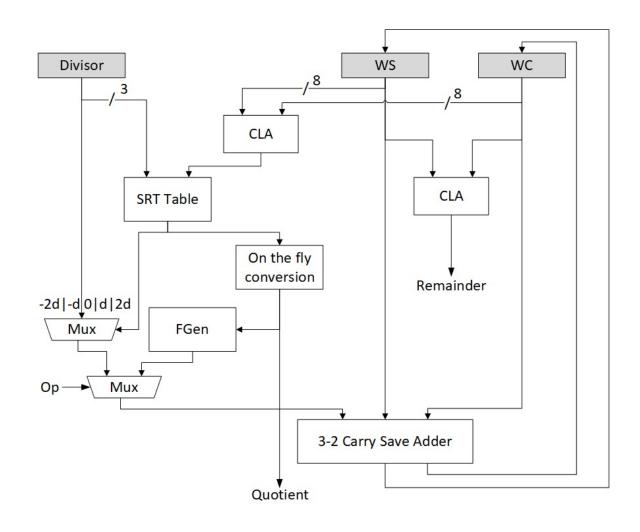

### ⇔ 定浮点除法/开方器

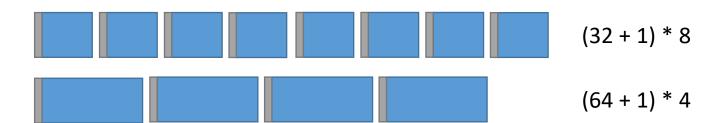

- 每周期可计算2-bit商

- 浮点开方/除法均采用SRT4 算法,共享商选择表

- 定点SRT4除法器不包括开 方部分,进行了shift over zero优化

北京微核芯科技有限公司 提供产业经验、联合完成结构设计及物理设计

#### 招募香山处理器二期联合开发合作伙伴

欢迎更多伙伴加入!

联系人:李迪13811881360

# 敬请批评指正!