中国开放指令生态(RISC-V)联盟 China RISC-V Alliance

# Practice of High-performance Chip Agile Development with Chisel

Yinan Xu 徐易难

ICT, CAS

xuyinan@ict.ac.cn

2021/6/26@CCC2021

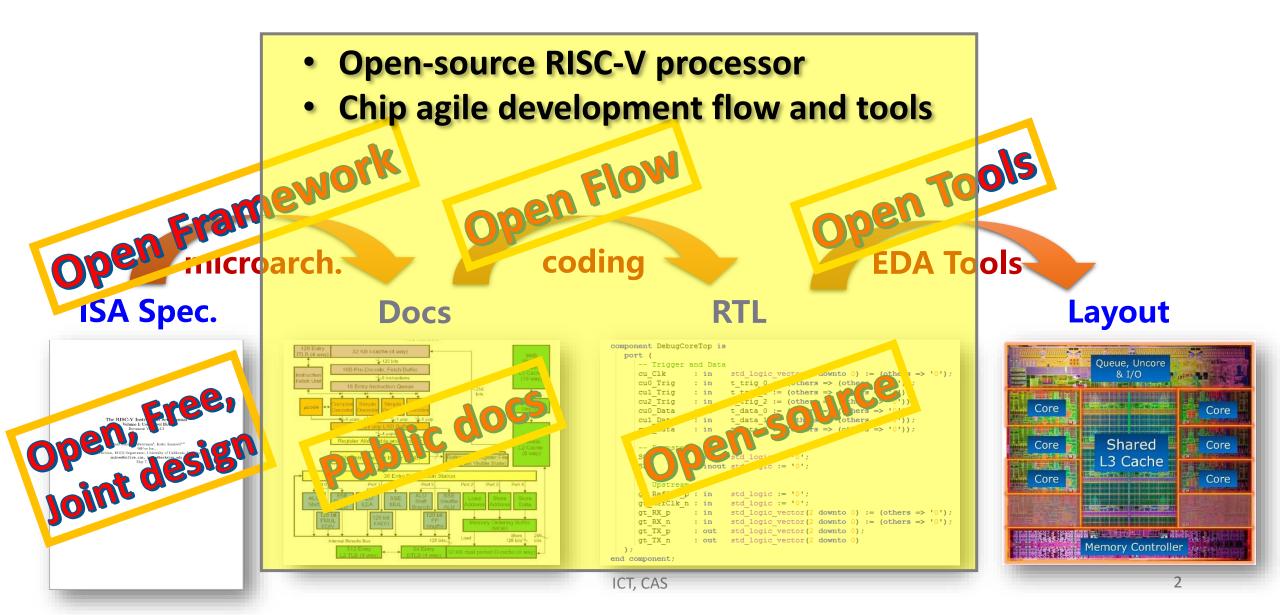

#### Open-source processor

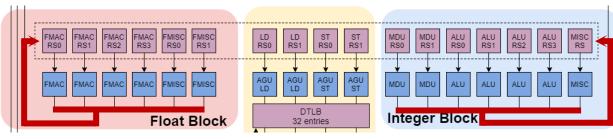

## XiangShan: a high-performance processor in Chisel

#### • 2020-2021: one processor in one year

- RV64GC ISA support

- 11-stage, superscalar, out-of-order, dual-core

- 5.3 CoreMark/MHz (gcc-9.3.0, -O2)

- Using a lot of **open-source tools/designs**

- Chisel/FIRRTL

- Verilator

- rocket-chip (parameters, diplomacy, TL/AXI4 nodes, ...)

- DRAMsim

- SiFive block inclusive cache

- Berkeley-hardfloat

- Open-sourced at GitHub/Gitee/Trustie/ihub

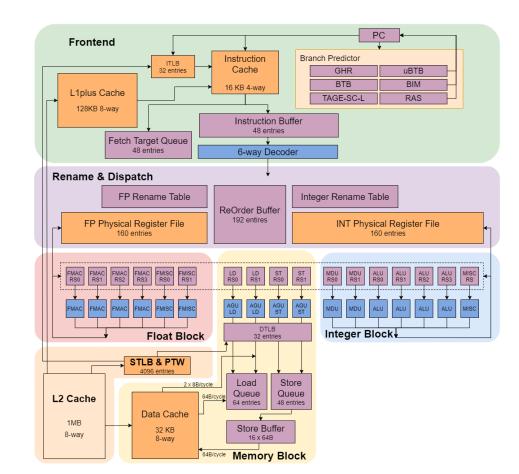

XiangShan (yanqihu) microarchitecture

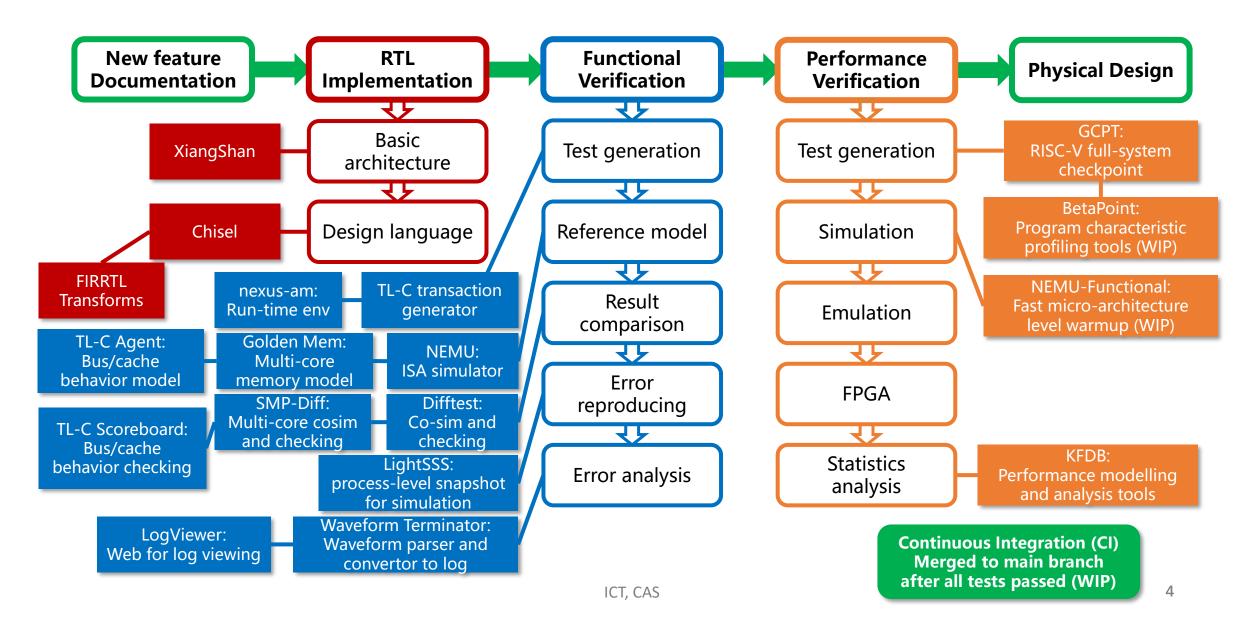

## Agile development infrastructures

## Agile development with Chisel

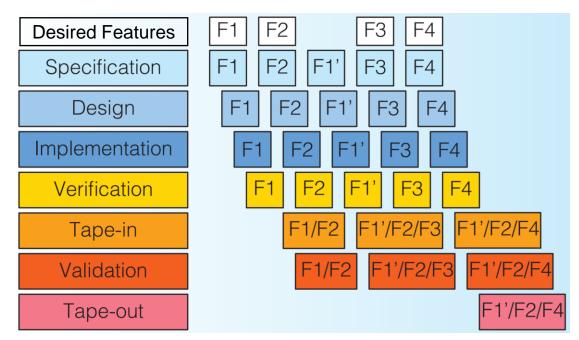

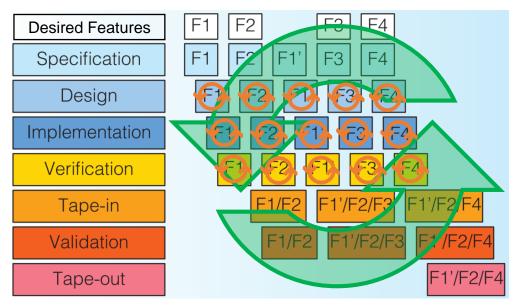

- Agile development: iterative, incremental, and evolutionary [1]

- How Chisel helps to survive in a rapidly-changing world

Agile model of hardware design [2]

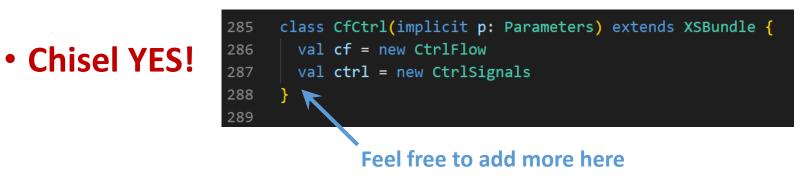

## Bundles: freely packaging signals

- Instructions are decoded into micro-ops and go through the pipeline

- Complex processors define a complex micro-op format

- Tens of signals with different widths

- Structuralized control signals (generated, used, dropped at different stages)

• SystemVerilog interface YES!

## **SystemVerilog interface YES?**

#### • Fine. Forget about the structuralized info.

Specifying modport for interface inside an interface in SystemVerilog Asked 5 years ago Active 5 years ago Viewed 1k times

|  | I have two interfaces with modports and another interface which cor<br>shown below:                                                                                                                                                                                                                                        | mbines these two interfaces as                        | The Overfl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | <pre>interface my_interface1<br/>// Some signals<br/>modport tb_to_dut (<br/>// Signal directions specified<br/>)<br/>endinterface<br/>interface my_interface2<br/>// Some signals<br/>modport tb_to_dut (<br/>// Signal directions specified<br/>)<br/>endinterface<br/>interface my_interface1<br/>interface linf1</pre> |                                                       | <ul> <li>Using faster</li> <li>Podca explain</li> <li>Featured c</li> <li>Take the second s</li></ul> |

|  | my_interface1 inf2<br>endinterface                                                                                                                                                                                                                                                                                         |                                                       | 829 How<br>851 Wha<br>inter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|  | I wanted to specify a modport for the combined interface which in te<br>the individual interfaces. The idea is as shown below.                                                                                                                                                                                             | urn calls/uses the modport of                         | 581 Inter<br>1475 Inter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|  | interface my_combined_interface<br>my_interface1 inf1<br>my_interface2 inf2                                                                                                                                                                                                                                                |                                                       | 1839 Wha<br>and<br>5 Rest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|  | <pre>modport tb_to_dut (     inf1.tb_to_dut,     inf2.tb_to_dut )</pre>                                                                                                                                                                                                                                                    |                                                       | 2 How                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|  | endinterface                                                                                                                                                                                                                                                                                                               | and the second section the                            | 1 Inter<br>1 Syste                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|  | This currently results in a syntax error. Is there a way by which I can s<br>combined interface such that it percolates down to the individual int                                                                                                                                                                         |                                                       | dk w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|  | interface system-verilog                                                                                                                                                                                                                                                                                                   |                                                       | How can I     control it                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|  | Share Follow                                                                                                                                                                                                                                                                                                               | asked May 25 '16 at 18:47 Pulimon 1,708 • 3 • 29 • 44 | Is it suspic<br>at the spe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Question: I have two interfaces with modports and another interface which combines these two interfaces. I wanted to specify a modport for the combined interface which in turn calls/uses the modport of the individual interfaces.

问: 我希望将两个接口组合到一起, 并使用他们定义的信号组成 一个新的模块接口定义

Unfortunately, SystemVerilog interface s lack compositional gualities and there is no way to specify an interface in pieces. The only way to do this today is to flatten out the combined interface 3 by bringing the lower level interface signals up to the top level. And I would avoid using modports altogether for the testbench.

Share Follow

5

#### Answer: The only way to do this today is to flatten out the interface. 答:唯一可以实现组合的方法,是把下层信号摊平,都放到顶层

Source: https://stackoverflow.com/questions/37445330/specifying-modport-for-interface-inside-an-interface-in-systemverilog

answered May 25 '16 at 20:45 dave 59

**30.7k** • 3 • 22 • 48

#### Parameterization

- Sometimes we need to change the parameters of the processor

- A different replacement policy

- A larger re-order buffer

- A unified reservation station (from a distributed reservation station)

- A wider rename pipeline width (multiple modules affected)

- They cause changes to different levels of the design

| Series/Scope    | Wire<br>Assignments | Internal logics | Module IOs | Module-level<br>Organizations | Example                      |

|-----------------|---------------------|-----------------|------------|-------------------------------|------------------------------|

| Youth           | மீ                  |                 |            |                               | Replacement policy           |

| Normal          | மீ                  | 凸               |            |                               | Queue size                   |

| Ultra           | மீ                  | 凸               | 凸          |                               | Enqueue width of a queue     |

| [BRAND] Edition | மீ                  | 凸               | 凸          | 凸                             | Decode/Rename/Dispatch width |

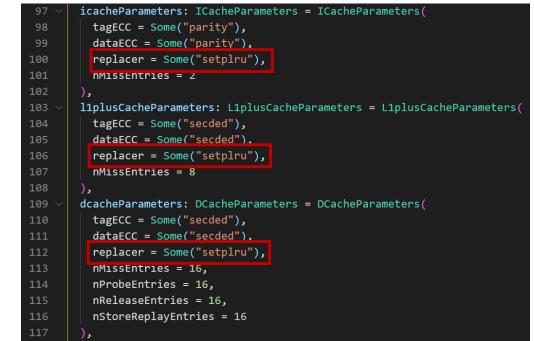

#### Parameterization Youth

- Between modules/methods with the same IO ports

- Example: replacement policy, error detection/correction

| 29 | 9 object ReplacementPolicy {                                                                        |  |  |  |  |

|----|-----------------------------------------------------------------------------------------------------|--|--|--|--|

| 30 | //for fully associative mapping                                                                     |  |  |  |  |

| 31 | <pre>def fromString(s: Option[String],n_ways: Int): ReplacementPolicy = fromString(s.getOrEl;</pre> |  |  |  |  |

| 32 | <pre>def fromString(s: String, n_ways: Int): ReplacementPolicy = s.toLowerCase match {</pre>        |  |  |  |  |

| 33 | <pre>case "random" =&gt; new RandomReplacement(n_ways)</pre>                                        |  |  |  |  |

| 34 | case "lru" => new TrueLRU(n_ways)                                                                   |  |  |  |  |

| 35 | case "plru" => new PseudoLRU(n_ways)                                                                |  |  |  |  |

| 36 | <pre>case t =&gt; throw new IllegalArgumentException(s"unknown Replacement Policy type \$t")</pre>  |  |  |  |  |

| 37 | }                                                                                                   |  |  |  |  |

| 38 | //for set associative mapping                                                                       |  |  |  |  |

| 39 | <pre>def fromString(s: Option[String], n_ways: Int, n_sets: Int): SetAssocReplacementPolicy =</pre> |  |  |  |  |

| 40 | <pre>def fromString(s: String, n_ways: Int, n_sets: Int): SetAssocReplacementPolicy = s.toLow</pre> |  |  |  |  |

| 41 | <pre>case "random" =&gt; new SetAssocRandom(n_sets, n_ways)</pre>                                   |  |  |  |  |

| 42 | <pre>case "setIru" =&gt; new SetAssocLRU(n_sets, n_ways, "lru")</pre>                               |  |  |  |  |

| 43 | <pre>case "setplru" =&gt; new SetAssocLRU(n_sets, n_ways, "plru")</pre>                             |  |  |  |  |

| 44 | <pre>case t =&gt; throw new IllegalArgumentException(s"unknown Replacement Policy type \$t")</pre>  |  |  |  |  |

| 45 | }                                                                                                   |  |  |  |  |

| 46 | }                                                                                                   |  |  |  |  |

#### (1) Implement all possibilities

#### (2) Use one line of code to choose one of them

#### Parameterization

- Between different structure sizes (e.g., queue size)

- usually only the pointer width is affected

| 11 < class FtqPtr(implicit p: Parameters) extends CircularQueuePtr[FtqPtr](         |

|-------------------------------------------------------------------------------------|

| 12 p => p(XSCoreParamsKey).FtqSize                                                  |

| 13 🗸 ){                                                                             |

| 14 override def cloneType = (new FtqPtr).asInstanceOf[this.type]                    |

| 15 }                                                                                |

| 16                                                                                  |

| 17 ${\scriptstyle 	imes}$ object <code>FtqPtr {</code>                              |

| <pre>18 \cong def apply(f: Bool, v: UInt)(implicit p: Parameters): FtqPtr = {</pre> |

| 19 val ptr = Wire(new FtqPtr)                                                       |

| 20 ptr.flag := f                                                                    |

| 21 ptr.value := v                                                                   |

| 22 ptr                                                                              |

| 23 }                                                                                |

| 24 }                                                                                |

|                                                                                     |

| 161<br>162<br>163<br>164<br>165 | <pre>// multi-write val update_target = Reg(Vec(FtqSize, JInt(VAddrBits.W))) val cfiIndex_vec = Reg(Vec(FtqSize, ValidUndirectioned(UInt(log2Up(PredictWidth).W)))) val cfiIsCall, cfiIsRt, cfiIsJalr, cfiIsRVC = Reg(Vec(FtqSize, Bool())) val mispredict_vec = Reg(Vec(FtqSize, Vec(PredictWidth, Bool())))</pre> |  |  |  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                 |                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 172 🗸                           | <pre>when(real_fire) {</pre>                                                                                                                                                                                                                                                                                        |  |  |  |

| 173                             | val enqIdx = tailPtr.value LinJiawei, 5 months ago • [WIP] fix ftq update logic                                                                                                                                                                                                                                     |  |  |  |

| 174                             | <pre>commitStateQueue(enqIdx) := VecInit(io.enq.bits.valids.map(v =&gt; Mux(v, s_valid, s_invalid)))</pre>                                                                                                                                                                                                          |  |  |  |

| 175                             | cfiIndey_vec(enqIdx) := io.enq.bits.cfiIndex                                                                                                                                                                                                                                                                        |  |  |  |

| 176                             | cfiIsCall(enqIdx) := ip.enq.bits.cfiIsCall                                                                                                                                                                                                                                                                          |  |  |  |

| 177                             | cfiIsRet(enqIdx) := ic.enq.bits.cfiIsRet                                                                                                                                                                                                                                                                            |  |  |  |

| 178                             | cfiIsJalr(enqIdx) := io.enq.bits.cfiIsJalr                                                                                                                                                                                                                                                                          |  |  |  |

| 179                             | cfiIsRV((enqIdx) := ic.enq.bits.cfiIsRVC                                                                                                                                                                                                                                                                            |  |  |  |

| 180                             | <pre>mispredict_vec(enqIdx) := WireInit(VecInit(Seq.fill(PredictWidth)(false.B)))</pre>                                                                                                                                                                                                                             |  |  |  |

| 181                             | update_1arget(enqIdx) := io.enq.bits.target                                                                                                                                                                                                                                                                         |  |  |  |

| 182                             | }                                                                                                                                                                                                                                                                                                                   |  |  |  |

(1) Define the parameterized queue size and queue pointer

(2) Use queue size to generate registers/wires and queue pointers to index into the queue

#### Parameterization Ultra

- We need a parameterized scheduler

- # total entries

- # selected entries

- Both IO ports and internal signals need parameterization

- Data width for input, output, wire, reg, ...

- Number of IO ports, wires, regs, ...

- How to express these in SystemVerilog and Chisel?

| <pre>module select(</pre>            |  |  |  |  |

|--------------------------------------|--|--|--|--|

| input [63:0] request,                |  |  |  |  |

| output [63:0] grant_0,               |  |  |  |  |

| output [63:0] grant_1,               |  |  |  |  |

| output [ <mark>63:0</mark> ] grant_2 |  |  |  |  |

| );                                   |  |  |  |  |

| // module body here                  |  |  |  |  |

| endmodule                            |  |  |  |  |

Verilog example for select logic

## Chisel: SystemVerilog generate Pro Max

- Parameterized scheduler: # total entries, # selected entries

- How to express these in SystemVerilog and Chisel?

```

interface select port #(

parameter NUM ENTRIES = 4

);

logic [NUM_ENTRIES - 1 : 0] grant;

modport sel iface(output grant);

endinterface

interface scheduler interface #(

parameter NUM ENTRIES = 64.

parameter NUM SELECT = 3

);

logic [NUM_ENTRIES - 1 : 0] request;

genvar i;

generate

for (i = 0; i < NUM SELECT; i++) begin</pre>

select port #(.NUM ENTRIES(NUM ENTRIES)) grants();

end

endgenerate

endinterface

```

```

class SelectPortIO(numEntries: Int) extends Bundle {

val grant = Output(UInt(numEntries.W))

}

class SchedulerIO(

numEntries: Int,

numSelect: Int

) extends Bundle {

val request = Input(UInt(numEntries.W))

val grant = Vec(numSelect, new SelectPort(numEntries))

}

```

Chisel

#### Chisel has fewer LOC and saves time.

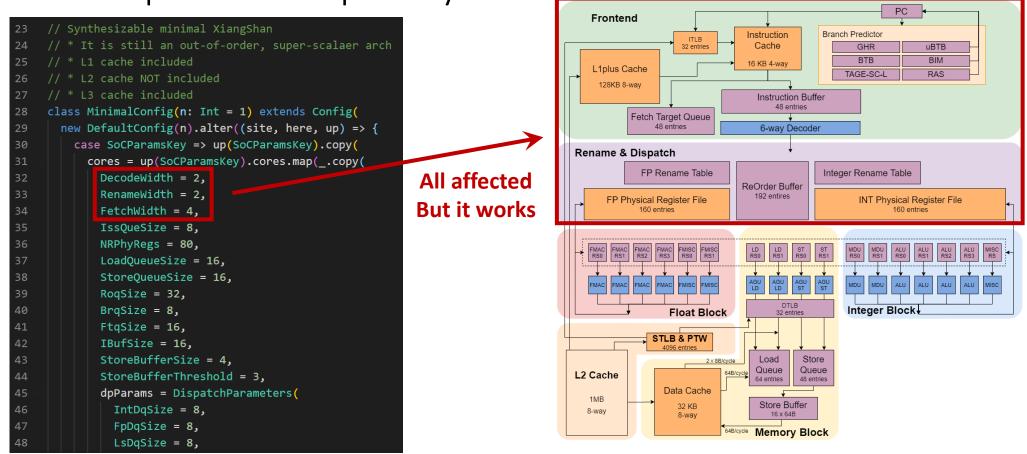

### Parameterization [some brand here] Edition

- Simply changing FetchWidth/DecodeWidth/RenameWidth to 4/2/2

- We didn't expect it to work perfectly

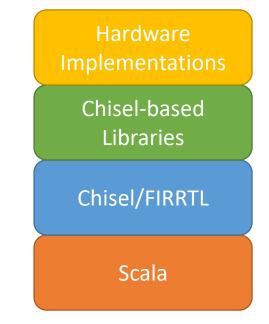

## More Chisel features for agile hardware development

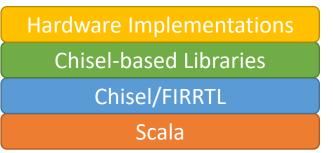

#### • Scala infrastructures

- Strong type system

- Full-featured IDEs from community

- Chisel/FIRRTL infrastructures

- SRAM type/size inference

- ChiselTest [1]

- FIRRTL transforms [2]

- Chisel-based Libraries

- Configs/Parameters

- Diplomacy framework

Levels of hardware development (with Chisel)

## Chisel for high-performance chip design

- Chisel efficiently produces structuralized and parameterized designs

- Fast, clear and simple

- But a lot of people have told us that they

- do NOT need agile development

- do NOT need parameterization

- care about ONLY the design quality

- How does Chisel ensure PPA?

## Weigh performance comes from the precise control of RTL

- Chisel is more like syntax sugar or an advanced generator for Verilog

- Chisel expressions strictly map to Verilog expressions

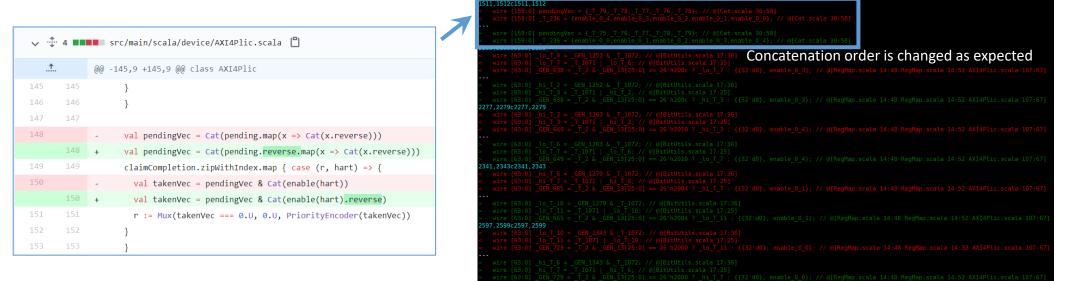

- Last month we fixed a bug that causes setting the PLIC claim register with a wrong value

- It's the designer that determines how the hardware works

- Chisel is not HLS. It does not translate/interpret what you write

- Chisel itself never hurts the PPA as well

#### • Then why Chisel? How does Chisel help ensure PPA?

#### Revisiting Chisel: what is it

- Chisel is a Scala-based advanced Verilog code generator

- Generating Verilog with Scala/Chisel libraries

- Rule-based code generation always works on Chisel

- Programming languages are primarily intended for expressing algorithms in a form that can be executed by a computer [1]

- Describe the rules in Scala and let Chisel generates the Verilog

- Example: auto-generated Wallace tree [2]

#### • Key: find the rules and use Chisel/Scala to describe it

<sup>[2]</sup> Jiawei Lin. Implementation of a Highly Configurable Wallace Tree Multiplier with Chisel. CCC2021.

### How Chisel helps high-performance designs

- Complexities cause difficulties in high-performance designs

- Wider: pipeline width changes from scalar to superscalar

- More complex: more pipelines, more structures

- Most logics in microarchitecture designs can be expressed by rules

- Duplications: decoders, ALUs, FMAs

- Dependences: branch predictors, selections, arbiters

- Most logics are either parallel or serialized

- Chisel easily generates complex but deterministic logics

- Because it is built on Scala programming language

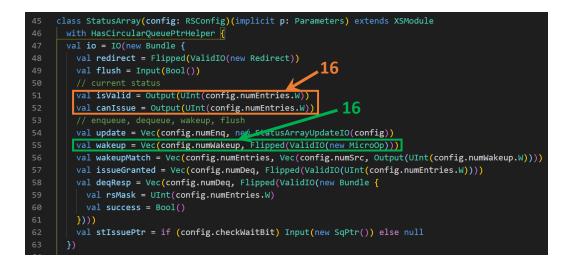

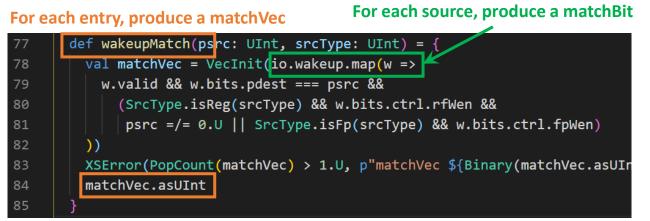

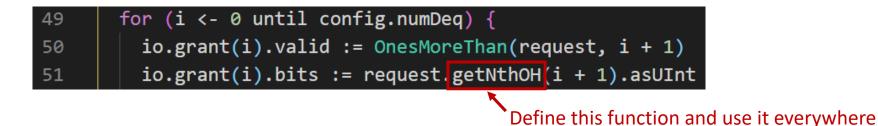

### Duplications: wakeup

- Wakeup in reservation stations

- Not-ready instructions wait in the RS

- Executed instructions wake them up

- >10 wakeup sources

Wakeup sources from RS/FU

- What to do: compare the producers' pdest with consumers' psrc

- Store Data RS: 16-entry RS, 8 integer + 8 FP wakeup ports

## Serialized logics: issue selection

- Issue: select the *n*-th one from a bit vector of length *m*

- Algorithm (for software)

- Let matrix[*m*][*n*] be whether first *m* bits has *n* ones

- If n is 0, matrix[m][n] = (whether first m bits has zero ones) = !bits.take(m).orR

- Otherwise, matrix[*m*][n] = bits[*m* 1] && matrix[*m* 1][*n* 1] || !bits[*m* 1] && matrix[*m* 1][*n*]

- Issue Grant Vector = bits & matrix[:][n 1]

- In Chisel, it's also allowed to recursively generate Verilog based on above rules

- But recursion never really happens in Verilog

ICT, CAS

### Chisel makes RTL coding faster

- Case study: rewriting RS in three days

- Modules: wakeup, select, status, payload, ...

- Without enqNum/deqNum parameterization

- Correctly running CoreMark

#### • Chisel: reducing the RTL coding time

- Scala for expressing the rules/algorithms

- Chisel libraries for generating the Verilog code

- Let computers do the boring job

- No more genvar, generate, begin...end keywords

- No more worries about whether it's synthesizable

- The fundamental advantage of Chisel against Verilog

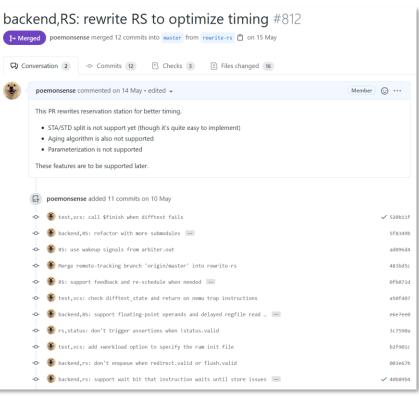

#### RS[1]: a case for agile development

## Put it all together: agile development with Chisel

- Requirements for **better agile development flows**

- To speed up every single step

- To shorten the overall iterative process

- Chisel approaches to agile development

- Abstraction (bundles), parameterization, module re-use

- A lot of Chisel/Scala infrastructures

....

• Scala-based advanced code generation

Agile model of hardware design [1]

• Chisel: more optimizing iterations in a fixed time interval

ICT. CAS

- Chisel significantly reduces the RTL coding time

- Faster than using Verilog/SV for iterative development

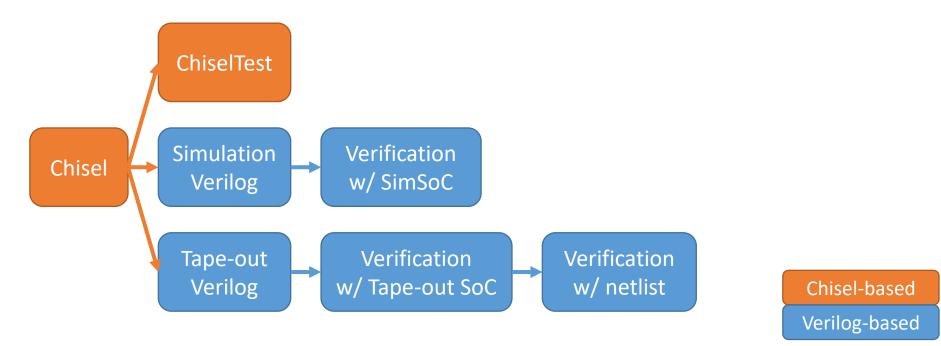

## XiangShan Tape-out (July 2021)

- Single XiangShan Core with 1MB L2 Cache

- 28nm HPCP, 1.3GHz@0.9V

- How does Chisel work in the tape-out process?

## Chisel: the learning curve

- People are not confused about Chisel itself

- chisel-cheatsheet [1] (2 pages) tells everything about Chisel

- Wire, Reg, := in Chisel are the same as wire, reg, assign in Verilog

- No always keyword in Chisel since assignments to Reg implicitly imply an always block

- Chisel itself does make RTL coding faster than ever before

- People are confused about advanced Scala features and Chisel-related libraries

- How to use object, abstract class, trait, ...

- How to use Parameters, Diplomacy, ...

- They are about how we build the software-level frameworks, not hardware

- They are not prerequisites for Chisel (and can be simply ignored if they cause difficulties)

- Start with plain Chisel only and learn Scala in the way to advanced agile development

- Only seven people in XiangShan team were experienced Chisel writers before June 2020

- But others, the Chisel beginners, have written/modified a lot of Chisel code as well by June 2021

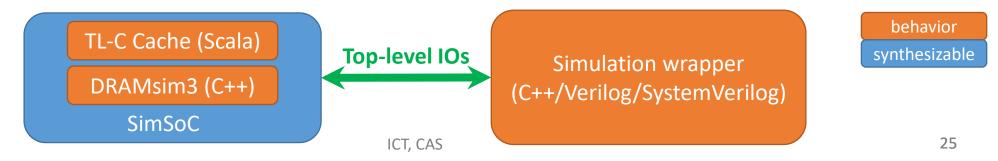

## Co-sim with behavior models

- There're always some behavior models

- Non-synthesizable C/C++/Verilog/SystemVerilog models

- FakePTW, RAMHelper, Difftest, DRAMsim3, ..., in XiangShan

- Models used in ChiselTest cannot be directly used when simulating other modules

- Chisel does not provide an elegant way to integrate them

- A dirty method: import and call DPI-C functions in a Blackbox Verilog module

- Dirty method creates many nearly empty modules and does not work for Scala models

- What if Scala models can both access to Chisel and be integrated into simulation

- Using behavior models to replace Chisel modules in simulation

- Only in the Scala programming language does the Tester/model know Chisel information

- Every line of code shares the structuralized and parameterized information in Chisel framework

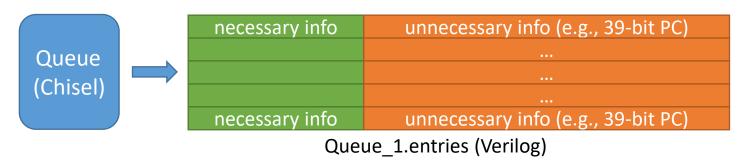

### Statistics for the generated Verilog

- We care about the size/elements of the structures in the processor

- Towards lower power level, less area, better energy efficiency

- Common structures: queues, SRAMs, tables, ...

- The size of the structures cannot be determined in Chisel source code

- Verilog is generated after many FIRRTL transforms

- Dead code elimination (DCE) removes some unused wires

- What if Chisel provides post-elaboration assertions or statistics

- Then we don't need to manually ensure there's no unexpected signal in Verilog

#### Better if we have

- assert(!entries.PC.exists)

- statistics(entries) along with the Verilog

### Intermediate variables in Chisel-generated Verilog

- A minor change in Chisel may result in more changes in Verilog than expected

- Chisel generates a lot of intermediate signals in Verilog

- They are mostly labeled \_T\_\*, \_GEN\_\*

- Different elaboration order generates different names

A little bit hard for physical design team to track how the RTL changes.

| ✓ + 4 ■                                 | src/main/scala/device/AXI4Plic.scala 🎒                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | oncatenation order is                                       |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

|                                         | @@ -145,9 +145,9 @@ class AXI4Plic                                                                                         | <pre>&gt; wire [159:0] pendingVec = {_T_75,_T_76,_T_77,_T_78,_T_79}; // @[Cat.scala 30:58]<br/>&gt; wire [159:0] _T_236 = {enable_0_0,enable_0_1,enable_0_2,enable_0_3,enable_0_4}; // @[Cat.scala 30:58]</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                   | hanged as expected                                          |

| 145 145                                 | }                                                                                                                          | <pre>&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                             |

| 146 146<br>147 147                      | }                                                                                                                          | <pre>&lt; wire [63:0] _lo_T_7 = _T_1071   _lo_T_6; // @[BitUtils.scala 17:25] </pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 14 40 Decker and 14 52 AVIAD in and 107 671                 |

| 147 147<br>148<br>149 149<br>150<br>150 | <pre>claimCompletion.zipWithIndex.map { case (r, hart) =&gt; {     val takenVec = pendingVec &amp; Cat(enable(hart))</pre> | <pre>&lt; wire [63:0] _GEN_638 = _T_2 &amp; _GEN_13[25:0] == 26'h200c ? _lo_T_7 : {{32'd0}, enable_0_3}; // @[RegMap.scala &gt; wire [63:0] _hi_T_2 = _GEN_1252 &amp; _T_1072; // @[BitUtils.scala 17:36] &gt; wire [63:0] _hi_T_3 = _T_1071   _hi_T_2; // @[BitUtils.scala 17:25] &gt; wire [63:0] _GEN_638 = _T_2 &amp; _GEN_13[25:0] == 26'h200c ? _hi_T_3 : {{32'd0}, enable_0_3}; // @[RegMap.scala 2277,2279c2277,2279 &lt; wire [63:0] _hi_T_2 = _GEN_1263 &amp; _T_1072; // @[BitUtils.scala 17:36] &lt; wire [63:0] _hi_T_3 = T_1071   _hi_T_2; // @[BitUtils.scala 17:36] &lt; wire [63:0] _hi_T_3 = T_1071   _hi_T_2; // @[BitUtils.scala 17:25]</pre> |                                                             |

| 151 151                                 | <pre>r := Mux(takenVec === 0.U, 0.U, PriorityEncoder(takenVec)) </pre>                                                     | <pre>&lt; wire [63:0] _GEN_649 = _T_2 &amp; _GEN_13[25:0] == 26'h2010 ? _hi_T_3 : {{32'd0}, enable 0.4} // @(RegMan_scale.)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 14:48 RegMan scala 14:52 AXIAPlic scala 107:671             |

| 152 152<br>153 153                      | Previous New                                                                                                               | <pre>&gt; wire [63:0] _GEN_649 = T_2 &amp; _GEN_13[25:0] == 26'h2010 ? _lo_T_7 : {{32'd0}, enable 2341,2343c2341,2343 &lt; wire [63:0] _hi_T_6 = _GEN_1279 &amp; T_1072; // @[BitUtils.scala 17:36] &lt; wire [63:0] _hi_T_6 = _GEN_1279 &amp; T_1072; // @[BitUtils.scala 17:36]</pre>                                                                                                                                                                                                                                                                                                                                                                           | name changes.<br>Inctional change.<br>Inges can be ignored. |

| _lo                                     | _T_6hi_T_2                                                                                                                 | <pre>&gt; wire [63:0] _lo_T_10 = _GEN_1279 &amp; _T_1072; // @[BitUtils.scala 17:36]<br/>&gt; wire [63:0] _lo_T_11 = _T_1071   _lo_T_10; // @[BitUtils.scala 17:25]<br/>&gt; wire [63:0] _GEN_665 = _T_2 &amp; _GEN_13[25:0] == 26'h2004 ? _lo_T_11 : {{32'd0}, enable_0_1}; // @[RegMap.scala</pre>                                                                                                                                                                                                                                                                                                                                                              | <u> </u>                                                    |

| _lo                                     | _T_7hi_T_3                                                                                                                 | 2597,2599c2597,2599<br>< wire [63:0] lo_T_10 = _GEN_1343 & _T_1072; // @[BitUtils.scala 17:36]<br>< wire [63:0] _lo_T_11 = _T_1071   _lo_T_10; // @[BitUtils.scala 17:25]<br>< wire [63:0] _GEN_20 = _T_1671   _lo_T_10; // @[BitUtils.scala 17:25]                                                                                                                                                                                                                                                                                                                                                                                                               | 14.49 PorWer coals 14.53 AVIADic coals 107.671              |

| _hi                                     | _T_2 _1o_T_6                                                                                                               | <pre>&lt; wire [63:0] _GEN_729 = _T_2 &amp; _GEN_13[25:0] == 26'h2000 ? _lo_T_11 : {{32'd0}, enable_0_0}; // @[RegMap.scala &gt; wire [63:0] _hi_T_6 = _GEN_1343 &amp; _T_1072; // @[BitUtils.scala 17:36] &gt; wire [63:0] _hi_T_7 = _T_1071   _hi_T_6; // @[BitUtils.scala 17:25]</pre>                                                                                                                                                                                                                                                                                                                                                                         |                                                             |

| _hi                                     | _T_3                                                                                                                       | <pre>&gt; wire [63:0] _GEN_729 = _T_2 &amp; _GEN_13[25:0] == 26'h2000 ? _hi_T_7 : {{32'd0}, enable_0_0}; // @[RegMap.scala ICT, CAS</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14:48 RegMap.scala 14:52 AXI4Plic.scala 107:67]             |

#### • Chisel can produce high-performance designs

- Chisel is an advanced HDL (not HLS)

- Chisel allows efficient structurization and parameterization

- Chisel itself never hurts PPA

#### • Chisel speeds up agile development

- Chisel provides an efficient RTL coding method

- More iterations in a fixed time interval

- More optimizations and possibly better PPA in a fixed time interval

#### • Chisel is imperfect but we can continuously improve it

• To do better on chip agile design, implementation and verification processes

中国开放指令生态(RISC-V)联盟 China RISC-V Alliance

# Thanks!

#### Welcome more people to join us on the 2<sup>nd</sup> generation of XiangShan!