Lin Jiawei

Institute of Computing Technology, Chinese Academy of Sciences

2021/6/26

source code

- 'printf' is a useful Chisel tool to debug circuits

- 'printf' can be translated to 'fwrite' in Verilog

- But it will slow down the simulation

- I/O overhead

- We need 'args', which may affect dead code elimination (dce)

```

case class Print(info: <u>Info</u>, string: <u>StringLit</u>, args: Seq[<u>Expression</u>], clk: <u>Expression</u>, en: <u>Expression</u>)

```

- There may be many 'printf' in a large chisel design

- X GB/min logs may be generated by 'printf' statements in a large design

- Hard to save

- Hard to analysis

- We usually only need some small parts of all 'printf' statements

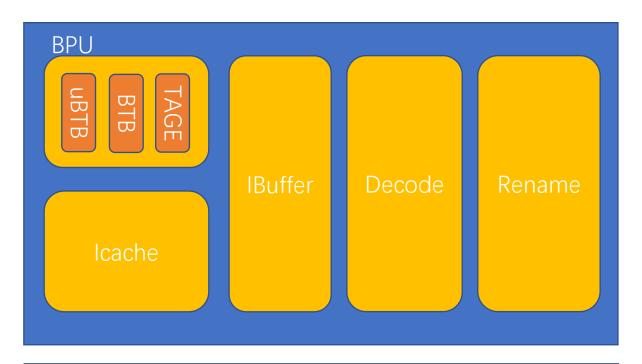

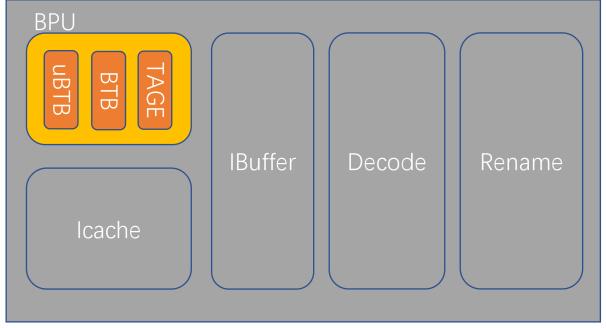

- Example: Only BPU's 'printf' in a large out-of-order processor when debugging branch predictors

- Can we disable/enable 'printf' in a specific module and its submodule by some parameters?

- Firrtl transform can help us

- Pass module names by annotations, then we can process them in a custom transform

- No need to modify Chisel source code!

## Implementation

- Define annotations

- Add command line options

- Write a custom Firrtl transform

### Implementation

- We defined 4 types of annotations

- DisablePrintfAnnotation

- EnablePrintfAnnotation

- DisableAllPrintAnnotation

- RemoveAssertAnnotation

- Each annotation has a corresponding command line option

```

case class DisablePrintfAnnotation(m: String) extends NoTargetAnnotation

object DisablePrintfAnnotation extends HasShellOptions{

27

val options = Seq(

29

new ShellOption[String](

longOption = "disable-module-print",

toAnnotationSeq = s => Seq(DisablePrintfAnnotation(s)),

32

helpText =

"The verilog 'printf' in the <module> and it's submodules will be removed\n",

shortOption = Some("dm"),

34

helpValueName = Some("<module>")

case class EnablePrintfAnnotation(m: String) extends NoTargetAnnotation

object EnablePrintfAnnotation extends HasShellOptions {

val options = Seq(

43

new ShellOption[String](

44

longOption = "enable-module-print",

toAnnotationSeq = s => Seq(EnablePrintfAnnotation(s)),

46

47

helpText =

"The verilog 'printf' except the <module> and it's submodules will be removed\n",

49

shortOption = Some("em"),

helpValueName = Some("<module>")

52

54

```

### Implementation

- We defined 4 types of annotations

- DisablePrintfAnnotation

- EnablePrintfAnnotation

- DisableAllPrintAnnotation

- RemoveAssertAnnotation

- Each annotation has a corresponding command line option

```

case class DisableAllPrintAnnotation() extends NoTargetAnnotation

object DisableAllPrintAnnotation extends HasShellOptions {

val options = Seq(

new ShellOption[Unit](

longOption = "disable-all",

toAnnotationSeq = _ => Seq(DisableAllPrintAnnotation()),

helpText =

"All the verilog 'printf' will be removed\n",

shortOption = Some("dall")

64

case class RemoveAssertAnnotation() extends NoTargetAnnotation

object RemoveAssertAnnotation extends HasShellOptions{

val options = Seq(

new ShellOption[Unit](

72

longOption = "remove-assert",

toAnnotationSeq = _ => Seq(RemoveAssertAnnotation()),

74

helpText = "All the 'assert' will be removed\n",

shortOption = None

79

```

#### Collect Annotations

```

override protected def execute(state: CircuitState): CircuitState = {

87

val disableList = state.annotations.collect {

case DisablePrintfAnnotation(m) => m

89

90

val enableList = state.annotations.collect {

91

92

case EnablePrintfAnnotation(m) => m

93

val disableAll = state.annotations.collectFirst {

94

95

case DisableAllPrintAnnotation() => true

}.nonEmpty

97

val removeAssert = state.annotations.collectFirst{

case RemoveAssertAnnotation() => true

99

}.nonEmpty

100

assert(!(enableList.nonEmpty && (disableAll | disableList.nonEmpty)))

101

```

## Analyze Circuit

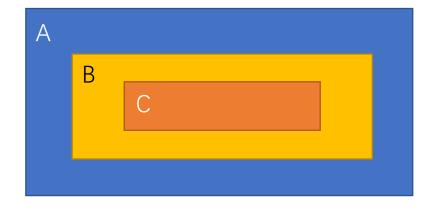

• ancestor(C) =  $\{A, B\}$

```

val c = state.circuit

val top = c.main

val queue = new mutable.Queue[String]()

val ancestors = new mutable.HashMap[String, mutable.LinkedHashSet[String]]()

queue += top

ancestors(top) = mutable.LinkedHashSet.empty

while (queue.nonEmpty) {

val curr = queue.dequeue()

c.modules.find(m => m.name==curr).foreach(m => {

def viewStmt(s: Statement): Statement = s match {

case DefInstance(_, _, module, _) =>

ancestors(module) = ancestors(curr) + m.name

queue += module

case other =>

other.mapStmt(viewStmt)

m.foreachStmt(viewStmt)

})

```

## Analyze Circuit

- firrtl.analyses.CircuitGraph is a better implementation

- Why not CircuitGraph?

- CircuiteGraph works with MidForm

- We want to run our transform with HighForm

- We haven't found a solution

## Modify Circuit

- For each module m

- If m is in the range that needs to be disabled, change Print statements to Empty statements

```

def onModule(m: DefModule): DefModule = m match {

case : ExtModule => m

case : Module =>

def inRange(seq: Seq[String]): Boolean = {

seq.nonEmpty && (seq.contains(m.name) | seq.map(elm => {

ancestors(m.name).contains(elm)

val enable = enableList.isEmpty | inRange(enableList)

val disable = disableAll | inRange(disableList) | !enable

def onStmt(s: Statement): Statement = s match {

case : Print if disable =>

EmptyStmt

case : Stop if removeAssert => EmptyStmt

case other => other.mapStmt(onStmt)

m.mapStmt(onStmt)

state.copy(circuit = c.mapModule(onModule))

```

## Example usage

- Command line args: -em BPU

- 'em' means **e**nable **m**odule print

- Only print statements in BPU and its submodule will be emitted to Verilog

## Thank You!