# **Internet Clock using PIC16F887**

# Ashwin Vallaban

Fr. Conceicao Rodrigues Institute of Technology, Vashi

Feb 2023

# **Table of Contents**

| 1 | Introdu  | ction and Summary of the Project                                           | 1    |

|---|----------|----------------------------------------------------------------------------|------|

| 2 | Design ( | Consideration                                                              | 3    |

|   | 2.1 Int  | roduction to PIC16F887                                                     | 3    |

|   | 2.1.1    | Memory Organization                                                        | 3    |

|   | 2.1.2    | IO Ports                                                                   | 4    |

|   | 2.1.3    | Configuration Bits (Fuses), Oscillator Selection and Basic Circuitry       | 5    |

|   | 2.2 Dis  | play driver                                                                | 8    |

|   | 2.2.1    | Introduction to MAX7219 display driver                                     | 8    |

|   | 2.2.2    | Interfacing MAX7219 with PIC16F887 using SPI protocol                      | 11   |

|   | 2.2.3    | Brightness control using ADC in PIC16F887                                  | 15   |

|   | 2.2.4    | Simulation Results                                                         | 16   |

|   | 2.3 Rea  | ll Time Clock                                                              | 17   |

|   | 2.3.1    | Introduction to RTC DS1307                                                 | 17   |

|   | 2.3.2    | Interfacing with PIC16F887 and I2C protocol                                | 18   |

|   | 2.3.3    | Simulation Results                                                         | 24   |

|   | 2.4 Into | ernet Time Synchronization                                                 | 25   |

|   | 2.4.1    | Introduction to ESP8266-01                                                 | 25   |

|   | 2.4.2    | Getting NTP time from the internet                                         | 25   |

|   | 2.4.3    | Interfacing PIC16F887 and ESP8266-01 using UART                            | 25   |

|   | 2.5 Usi  | ng Switch for setting time manually and all peripheral integration         | 29   |

| 3 | Compor   | ents and Electrical Specifications                                         | 32   |

|   | 3.1 Bill | of Materials                                                               | 32   |

|   | 3.2 MA   | X7219 and 7 Segment Display                                                | 32   |

|   | 3.2.1    | 7 Segment Display Absolute Ratings                                         | 32   |

|   | 3.2.2    | MAX7219 Electrical Characteristics, RSET and Power Dissipation Calculation | n 33 |

|   | 3.3 A/I  | Acquisition Time                                                           | 34   |

|   | 3.4 DS   | 1307 RTC                                                                   | 35   |

|   | 3.4.1    | Electrical Specifications of DS1307                                        | 35   |

|   | 3.4.2    | I2C pull-up resistor calculation                                           | 37   |

|   | 3.5 Usi  | ng 3.3V regulator for powering ESP8266-01                                  | 37   |

|   | 3.6 Pov  | ver Specification of Entire Project                                        | 38   |

| 1 | Doforon  |                                                                            | 20   |

# **Software Used**

| Software             | Version | Used for                       |

|----------------------|---------|--------------------------------|

| MPLAB X IDE          | 6.05    | Configuration Bits             |

| mikroC Pro           | 7.6.0   | PIC Programming                |

| QL-PROG for QL-2006  | 2.37    | PIC Burner                     |

| Proteus Design Suite | 8.9 SP2 | Simulation                     |

| Arduino IDE          | 1.8.19  | ESP-01 Programming with CP2102 |

|                      |         | UART Serial Converter          |

# Table of Figures

| Figure 1 General Overview of the Project              | 1  |

|-------------------------------------------------------|----|

| Figure 2 Block Diagram of Internet Clock              | 2  |

| Figure 3 Overall Simulation on Proteus.               |    |

| Figure 4 Program Memory Map of PIC16F886/7            | 3  |

| Figure 5 Special Function Registers                   |    |

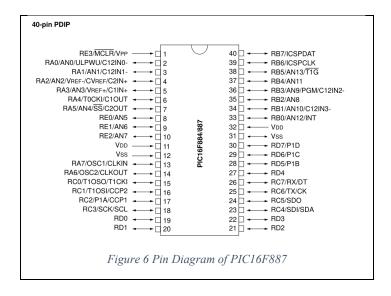

| Figure 6 Pin Diagram of PIC16F887                     | 5  |

| Figure 7 Configuration Register 1                     | 5  |

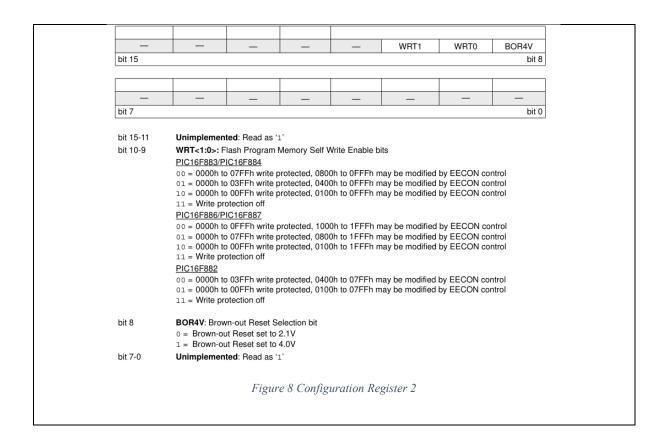

| Figure 8 Configuration Register 2                     | 6  |

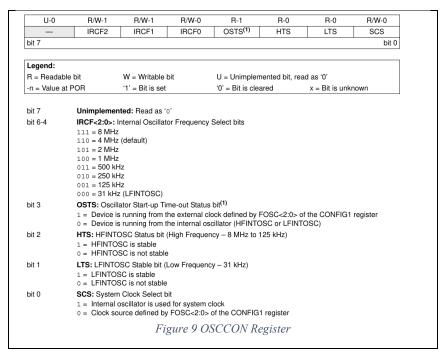

| Figure 9 OSCCON Register                              | 6  |

| Figure 10 Configuration Bits generated using MPLAB X  | 7  |

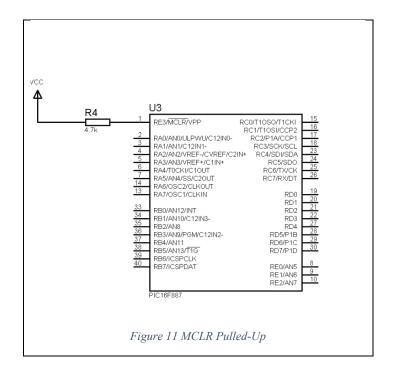

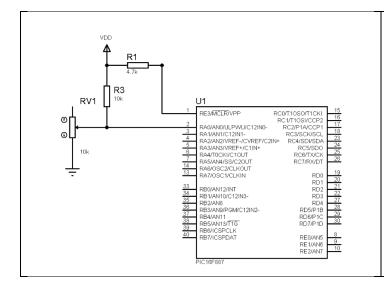

| Figure 11 MCLR Pulled-Up                              |    |

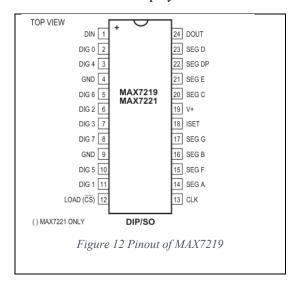

| Figure 12 Pinout of MAX7219                           | 8  |

| Figure 13 MAX7219 Pin Description                     | 8  |

| Figure 14 Serial-Data Format MAX7219                  | 9  |

| Figure 15 MAX7219 Register Address Map                | 9  |

| Figure 16 Decode-Mode Register Example MAX7219        | 10 |

| Figure 17 Code B Format MAX7219                       | 10 |

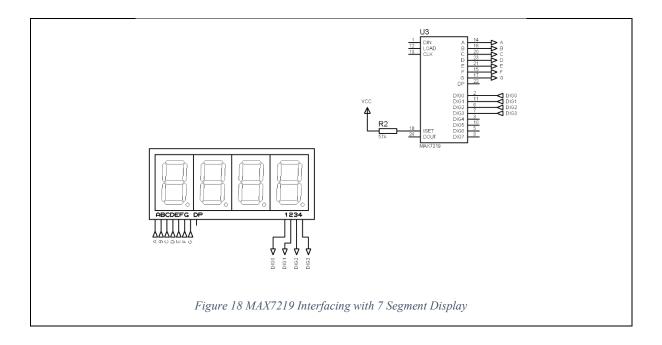

| Figure 18 MAX7219 Interfacing with 7 Segment Display  | 11 |

| Figure 19 SSPSTAT SSP Status Register                 | 12 |

| Figure 20 SSPCON Register                             | 13 |

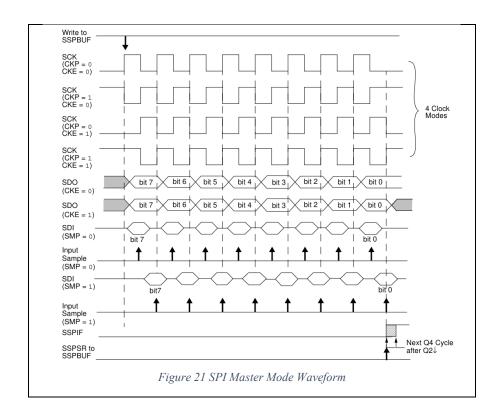

| Figure 21 SPI Master Mode Waveform                    | 14 |

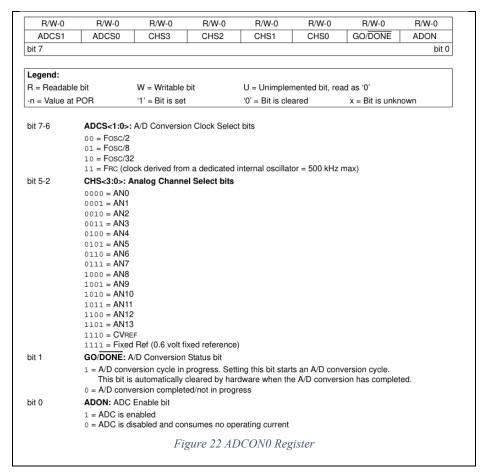

| Figure 22 ADCON0 Register                             | 15 |

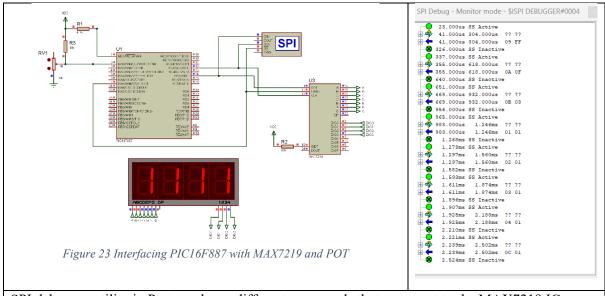

| Figure 23 Interfacing PIC16F887 with MAX7219 and POT  | 16 |

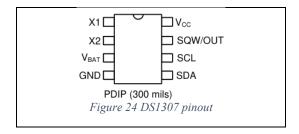

| Figure 24 DS1307 pinout                               | 17 |

| Figure 25 DS1307 pin description                      | 17 |

| Figure 26 DS1307 Registers                            | 18 |

| Figure 27 DS1307 Control Register                     | 18 |

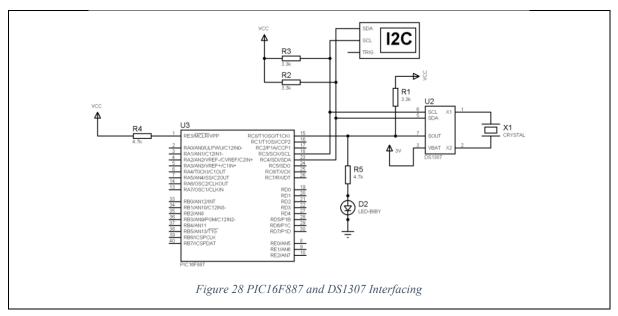

| Figure 28 PIC16F887 and DS1307 Interfacing            | 19 |

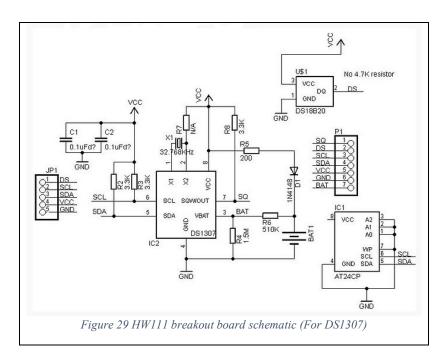

| Figure 29 HW111 breakout board schematic (For DS1307) | 19 |

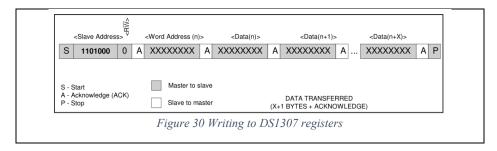

| Figure 30 Writing to DS1307 registers                 | 20 |

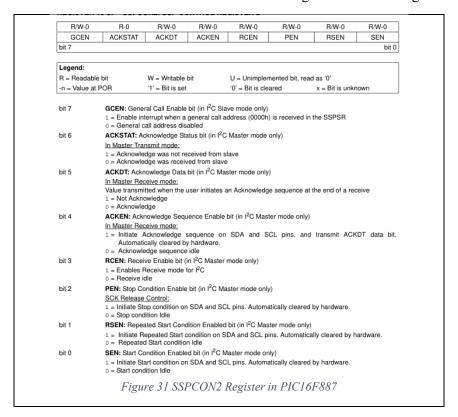

| Figure 31 SSPCON2 Register in PIC16F887               | 20 |

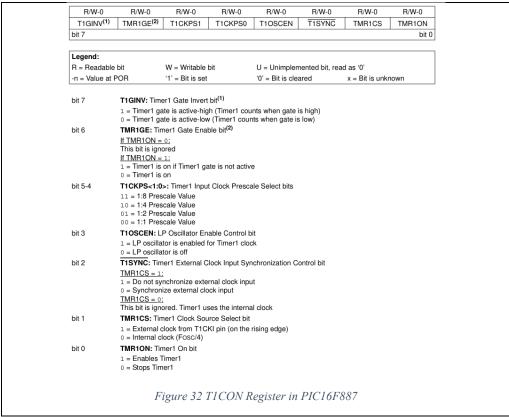

| Figure 32 T1CON Register in PIC16F887                 | 21 |

| Figure 33 INTCON Register PIC16F887                   | 22 |

| Figure 34 PIR1 Register PIC16F887                     | 23 |

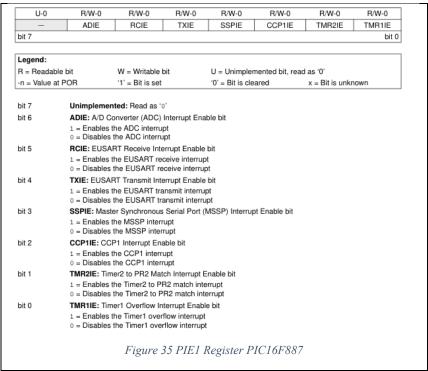

| Figure 35 PIE1 Register PIC16F887                     |    |

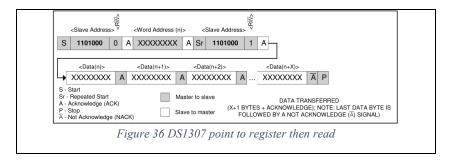

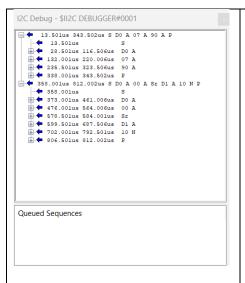

| Figure 36 DS1307 point to register then read          | 24 |

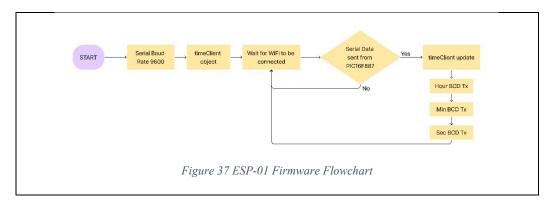

| Figure 37 ESP-01 Firmware Flowchart                   | 25 |

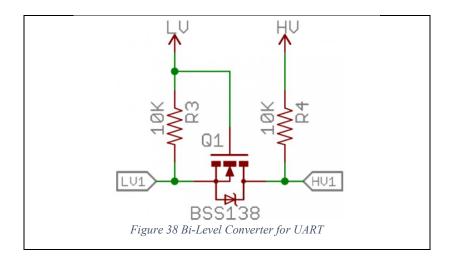

| Figure 38 Bi-Level Converter for UART                 | 26 |

| Figure 39 TXSTA Register in PIC16F887                 | 27 |

| Figure 40 RCSTA Register in PIC16F887                 | 27 |

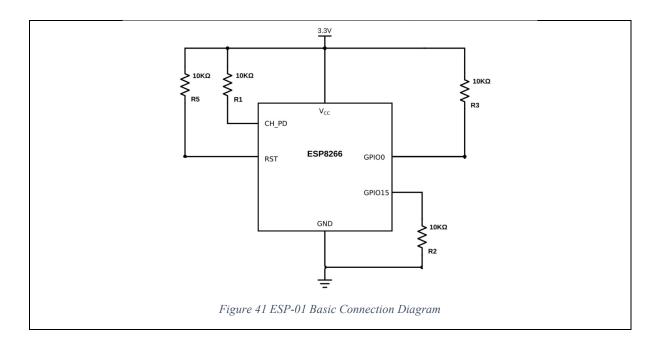

| Figure 41 ESP-01 Basic Connection Diagram             | 28 |

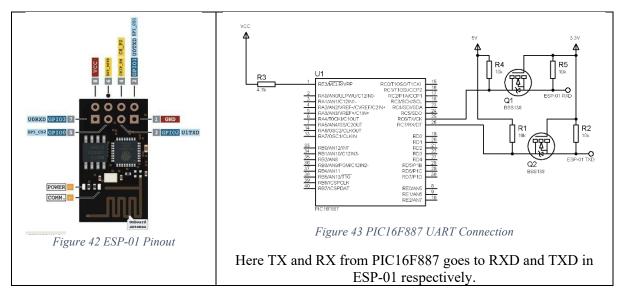

| Figure 42 ESP-01 Pinout                               | 28 |

| Figure 43 PIC16F887 UART Connection                   | 28 |

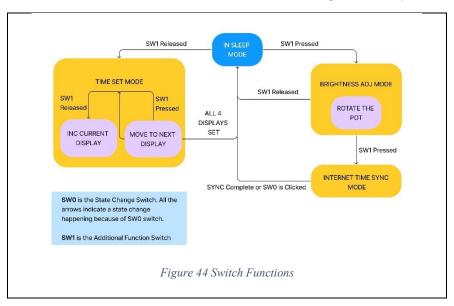

| Figure 44 Switch Functions                            | 29 |

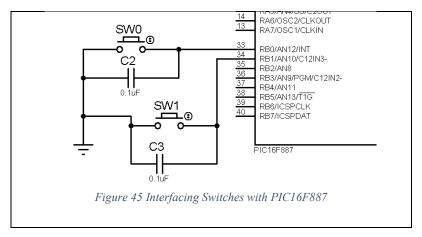

| Figure 45 Interfacing Switches with PIC16F887               | 29 |

|-------------------------------------------------------------|----|

| Figure 46 OPTION Register in PIC16F887                      | 30 |

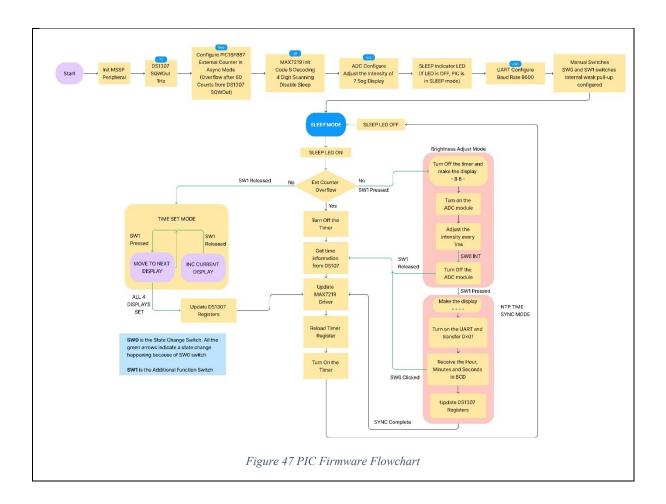

| Figure 47 PIC Firmware Flowchart                            | 31 |

| Figure 48 7 Segment Display Absolute Maximum Ratings        | 32 |

| Figure 49 MAX7219 Electrical Specification                  | 33 |

| Figure 50 RSET vs Segment Current and LED forward Voltage   | 33 |

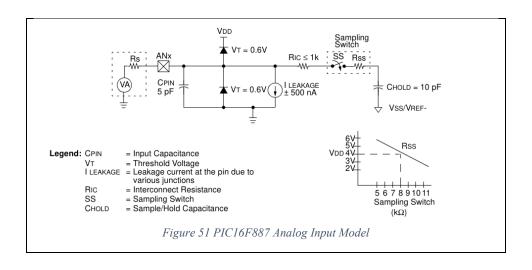

| Figure 51 PIC16F887 Analog Input Model                      | 35 |

| Figure 52 DS1307 recommended operating conditions           | 35 |

| Figure 53 DS1307 DC electrical characteristics (on supply)  | 35 |

| Figure 54 DS1307 DC electrical characteristics (on battery) | 36 |

| Figure 55 DS1307 AC characteristics                         | 36 |

| Figure 56 DS1307 Pin capacitance                            | 36 |

| Figure 57 DS1307 Crystal Specifications                     | 37 |

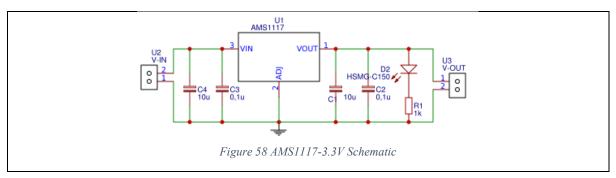

| Figure 58 AMS1117-3.3V Schematic                            | 37 |

|                                                             |    |

|                                                             |    |

|                                                             |    |

# **Table of Code Snippets**

| Code Snippet 1 SPI data transfer function (to MAX7219)   | 14 |

|----------------------------------------------------------|----|

| Code Snippet 2 Display Character '1' in MAX7219          | 14 |

| Code Snippet 3 Enable 1Hz SQWOutput on DS1307            | 20 |

| Code Snippet 4 60sec Counter with Sleep Mode             | 22 |

| Code Snippet 5 BCD to Decimal Conversion for TMR1H:TMR1L | 24 |

| Code Snippet 6 ESP-01 NTPClient Init                     |    |

| Code Snippet 7 UART Configure in PIC16F887               | 26 |

| Code Snippet 8 Switch Function                           |    |

|                                                          |    |

# 1 Introduction and Summary of the Project

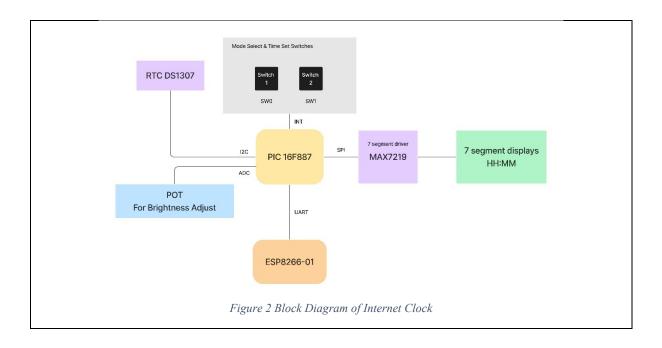

Internet Clock is a project which shows time in HH: MM. Although the firmware is also compatible with all the series of PIC16F88x, PIC16F887 is primarily described in this documentation. A Real Time Clock (RTC) IC is used to keep the track of time. Tactile switches are provided which can also be used to adjust the time manually. Clock can also be synchronized with the internet time using a Wi-Fi module (ESP8266-01). The time is displayed on 7 segment displays driven by a display driver. A Potentiometer is used to set the brightness of the 7 segment displays using the measured ADC value.

### Peripherals used:

- I2C between PIC and RTC

- UART between PIC and Wi-Fi module

- **SPI** between PIC and 7 segment display driver

- **ADC** for measuring the POT value

- Timer/counter in PIC for keeping track of seconds elapsed

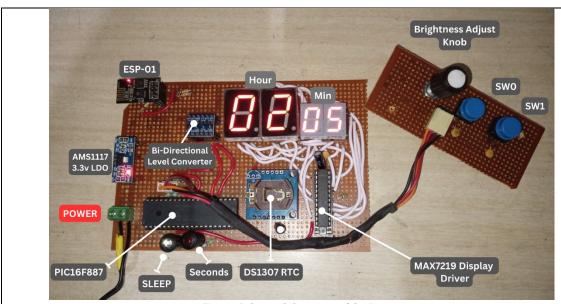

Figure 1 General Overview of the Project

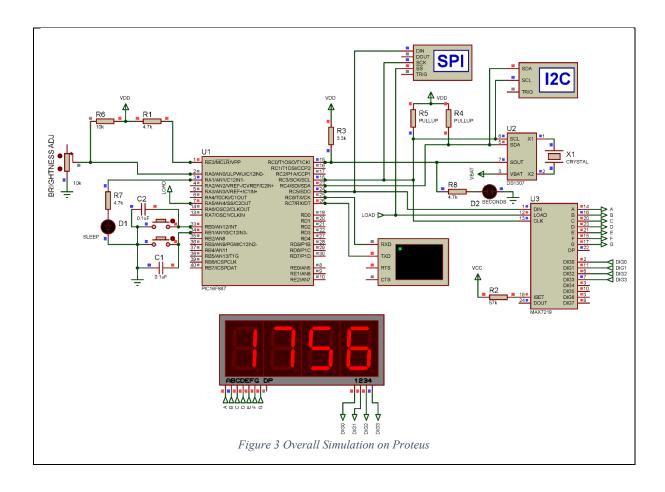

Figure 2 shows the block diagram of the Internet Clock Project. The overall simulation in Proteus is shown in figure 3.

# 2 Design Consideration

#### 2.1 Introduction to PIC16F887

### 2.1.1 Memory Organization

PIC16F88x series microcontroller is offered by Microchip. As quoted in their datasheet, it is a 28/40/44-Pin, Enhanced Flash-Based 8-Bit CMOS Microcontrollers with nanoWatt Technology. This project uses PIC16F887 which is a 8-bit midrange microcontroller. Some of the features which lead to using this microcontroller for the project was:

- Internal Precision Oscillator with range 8MHz to 31kHz which can be tuned with software

- Power saving sleep mode

- Power On Reset (POR)

- Oscillator Start-up Timer (OST)

- 8K Bytes Program Memory (Flash Word of 14 bit)

- 368 Bytes SRAM

- 10-bit ADC

- 8-bit and 16-bit Timer/Counter

- Master Synchronous Serial Port (MSSP) supporting I2C and SPI

- Enhanced USART

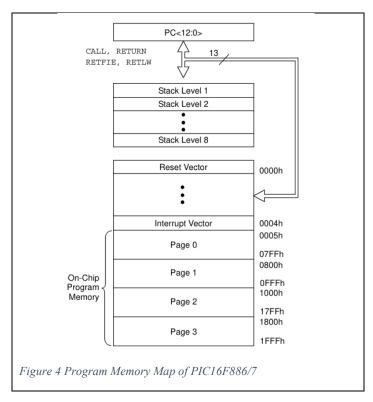

It has a 13-bit Program Counter (PC) addressing from 0000h to 1FFFh. Reset vector is at 0000h and Interrupt vector is at 0004h.

Data memory is partitioned into 4 banks ranging from 000h to 1FFh. It consists of General-Purpose Registers (GPR) and Special Function Registers (SFR). The SFR is located in the first 32 locations of each bank. GPR are located in the last 96 locations of each bank. In order to select a bank, RP1 & RP0 bits in STATUS register <03h> is used.

|                      | File    |                      | File    |                    | File    |                    | File    |

|----------------------|---------|----------------------|---------|--------------------|---------|--------------------|---------|

|                      | Address |                      | Address |                    | Address |                    | Address |

| Indirect addr. (1)   | 00h     | Indirect addr. (1)   | 80h     | Indirect addr. (1) | 100h    | Indirect addr. (1) | 180h    |

| TMR0                 | 01h     | OPTION_REG           | 81h     | TMR0               | 101h    | OPTION_REG         | 181h    |

| PCL                  | 02h     | PCL                  | 82h     | PCL                | 102h    | PCL                | 182h    |

| STATUS               | 03h     | STATUS               | 83h     | STATUS             | 103h    | STATUS             | 183h    |

| FSR                  | 04h     | FSR                  | 84h     | FSR                | 104h    | FSR                | 184h    |

| PORTA                | 05h     | TRISA                | 85h     | WDTCON             | 105h    | SRCON              | 185h    |

| PORTB                | 06h     | TRISB                | 86h     | PORTB              | 106h    | TRISB              | 186h    |

| PORTC                | 07h     | TRISC                | 87h     | CM1CON0            | 107h    | BAUDCTL            | 187h    |

| PORTD <sup>(2)</sup> | 08h     | TRISD <sup>(2)</sup> | 88h     | CM2CON0            | 108h    | ANSEL              | 188h    |

| PORTE                | 09h     | TRISE                | 89h     | CM2CON1            | 109h    | ANSELH             | 189h    |

| PCLATH               | 0Ah     | PCLATH               | 8Ah     | PCLATH             | 10Ah    | PCLATH             | 18Ah    |

| INTCON               | 0Bh     | INTCON               | 8Bh     | INTCON             | 10Bh    | INTCON             | 18Bh    |

| PIR1                 | 0Ch     | PIE1                 | 8Ch     | EEDAT              | 10Ch    | EECON1             | 18Ch    |

| PIR2                 | 0Dh     | PIE2                 | 8Dh     | EEADR              | 10Dh    | EECON2(1)          | 18Dh    |

| TMR1L                | 0Eh     | PCON                 | 8Eh     | EEDATH             | 10Eh    | Reserved           | 18Eh    |

| TMR1H                | 0Fh     | OSCCON               | 8Fh     | EEADRH             | 10Fh    | Reserved           | 18Fh    |

| T1CON                | 10h     | OSCTUNE              | 90h     |                    | 110h    |                    | 190h    |

| TMR2                 | 11h     | SSPCON2              | 91h     |                    | 111h    |                    | 191h    |

| T2CON                | 12h     | PR2                  | 92h     |                    | 112h    |                    | 192h    |

| SSPBUF               | 13h     | SSPADD               | 93h     |                    | 113h    |                    | 193h    |

| SSPCON               | 14h     | SSPSTAT              | 94h     |                    | 114h    |                    | 194h    |

| CCPR1L               | 15h     | WPUB                 | 95h     |                    | 115h    |                    | 195h    |

| CCPR1H               | 16h     | IOCB                 | 96h     | General            | 116h    | General            | 196h    |

| CCP1CON              | 17h     | VRCON                | 97h     | Purpose            | 117h    | Purpose            | 197h    |

| RCSTA                | 18h     | TXSTA                | 98h     | Registers          | 118h    | Registers          | 198h    |

| TXREG                | 19h     | SPBRG                | 99h     | 16 Bytes           | 119h    | 16 Bytes           | 199h    |

| RCREG                | 1Ah     | SPBRGH               | 9Ah     | ,                  | 11Ah    |                    | 19Ah    |

| CCPR2L               | 1Bh     | PWM1CON              | 9Bh     |                    | 11Bh    |                    | 19Bh    |

| CCPR2H               | 1Ch     | ECCPAS               | 9Ch     |                    | 11Ch    |                    | 19Ch    |

| CCP2CON              | 1Dh     | PSTRCON              | 9Dh     |                    | 11Dh    |                    | 19Dh    |

| ADRESH               | 1Eh     | ADRESL               | 9Eh     |                    | 11Eh    |                    | 19Eh    |

| ADCON0               | 1Fh     | ADCON1               | 9Fh     |                    | 11Fh    |                    | 19Fh    |

|                      | 20h     |                      | A0h     |                    | 120h    |                    | 1A0h    |

|                      |         | General<br>Purpose   |         | General            |         | General            |         |

| General              | 3Fh     | Registers            |         | Purpose            |         | Purpose            |         |

| Purpose              | 40h     |                      |         | Registers          |         | Registers          |         |

| Registers            |         | 80 Bytes             |         | 80 Bytes           |         | 80 Bytes           |         |

| 96 Bytes             | 6Fh     |                      | EFh     | ,                  | 16Fh    | ,                  | 1EFh    |

| ,                    | 70h     | accesses             | F0h     | accesses           | 170h    | accesses           | 1F0h    |

|                      | 7Fh     | 70h-7Fh              | FFh     | 70h-7Fh            | 17Fh    | 70h-7Fh            | 1FFh    |

| Bank 0               |         | Bank 1               |         | Bank 2             |         | Bank 3             | '       |

#### **2.1.2 IO Ports**

IO pins may have different functionalities other than general purpose input output depending on the peripherals which are enabled. PIC16F887 consists of PORTA, PORTB, PORTC, PORTD & PORTE. Corresponding TRISx register is used to indicate if the PORTx pin will function as an input or an output. If TRISx = 1, the pin acts as an input and when TRISx = 0, the pin acts as an output. Configuring as an input disables the output driver driver and vice-versa. Writing to a port indicated writing to a latch which read operation reads the status of the port pin. All operations are Read-Modify-Write. Some port pins may be used as ADC input. ANSEL register <188h> is used to configure an Analog pin to be used as Digital I/O. Setting (=1) ANSEL register bit ANSx where x is the Analog Port selected makes the pin Analog while Clearing (=0) makes the pin Digital. Default state on Reset if Analog for all the compatible port pins.

## 2.1.3 Configuration Bits (Fuses), Oscillator Selection and Basic Circuitry

Configuration Bits or Fuses are programmed while burning the firmware onto the microcontroller. These bits are mapped to location 2007h. This location is beyond the user program memory space and can be only accessed while programming the chip. Configuration bits consists of CONFIG1 Register and CONFIG2 registers.

In the project Internal factory calibrated oscillator is used. The frequency can be varied from 8MHz to 31kHz. OSCCON Register <8Fh> is used to configure the oscillator while clock source is selected by setting the FOSC<2:0> bits in CONFIG1. For this project, 4MHz Internal Oscillator is used. For configuring the oscillator, CONFIG1 FOSC bits are set to 100 which is INTOSCIO mode so that I/O functions in RA6 and RA7 pins can be preserved. 4MHz is the default Internal Clock speed in the OSCCON Register <8Fh>. Low Voltage programming is not desired so the LVP bit is cleared.

PIC16F887 consists of an On-Chip Power-On Reset (POR). However, it also consists of a Brown-out Reset (BOR) which if enabled keeps the chip in Reset until VDD reached BOR. For the project BOR is enabled by setting BOREN to 1 and in the CONFIG2 register BOR4V is set to 1(BOR is 4V).

MCLR (Active Low) pin is used to Reset the PIC16F887. It has a noise filter which will ignore small pulses. Microchip recommends MCLR should not be connected directly to VDD and a resistor with  $1k\Omega$  or greater should be used. Internal MCLR option can be enabled by clearing the MCLRE bit in the CONFIG1 register. In the project MCLRE is set so RA3/MCLR pin becomes external reset with weak pull-up to VDD.

| Address | Name    | Value | Field | Option         | Category                                    | Setting                                                                  |

|---------|---------|-------|-------|----------------|---------------------------------------------|--------------------------------------------------------------------------|

| 2007    | CONFIG1 | 2FF4  | -     | -              | -                                           |                                                                          |

|         |         | 4     | FOSC  | INTRC_NOCLKOUT | Oscillator Selection bits                   | INTOSCIO oscillator: I/O function on RA6/OSC2/CLKOUT pin, I/O function o |

|         |         | 0     | WDTE  | OFF            | Watchdog Timer Enable bit                   | WDT disabled and can be enabled by SWDTEN bit of the WDTCON register     |

|         |         | 1     | PWRTE | OFF            | Power-up Timer Enable bit                   | PWRT disabled                                                            |

|         |         | 1     | MCLRE | ON             | RE3/MCLR pin function select bit            | RE3/MCLR pin function is MCLR                                            |

|         |         | 1     | CP    | OFF            | Code Protection bit                         | Program memory code protection is disabled                               |

|         |         | 1     | CPD   | OFF            | Data Code Protection bit                    | Data memory code protection is disabled                                  |

|         |         | 3     | BOREN | ON             | Brown Out Reset Selection bits              | BOR enabled                                                              |

|         |         | 1     | IESO  | ON             | Internal External Switchover bit            | Internal/External Switchover mode is enabled                             |

|         |         | 1     | FCMEN | ON             | Fail-Safe Clock Monitor Enabled bit         | Fail-Safe Clock Monitor is enabled                                       |

|         |         | 0     | LVP   | OFF            | Low Voltage Programming Enable bit          | RB3 pin has digital I/O, HV on MCLR must be used for programming         |

| 2008 (  | CONFIG2 | 3FFF  | -     | -              | -                                           | F                                                                        |

|         |         | 1     | BOR4V | BOR40V         | Brown-out Reset Selection bit               | Brown-out Reset set to 4.0V                                              |

|         |         | 3     | WRT   | OFF            | Flash Program Memory Self Write Enable bits | Write protection off                                                     |

### 2.2 Display driver

### 2.2.1 Introduction to MAX7219 display driver

For interfacing various 7 segment displays in the project MAX7219 chip is used. It supports interfacing up to 8 displays and can control each segments individually. It is compatible with SPI protocol. Brightness of each display can be controlled and a test mode is provided to check if the displays are working properly or not. It has an inbuilt oscillator which supports 10MHz serial interface. MAX7219 is usually used to drive Common-Cathode LED displays.

Using 4 wire serial interface (SPI), displays can be controlled intelligently. MAX7219 works on 5V with maximum current up to 330mA. Display scan rate can go from 500Hz till 1300Hz.

| PIN                  | NAME               | FUNCTION                                                                                                                                                                                                                                              |

|----------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                    | DIN                | Serial-Data Input. Data is loaded into the internal 16-bit shift register on CLK's rising edge.                                                                                                                                                       |

| 2, 3, 5–8,<br>10, 11 | DIG 0-DIG 7        | Eight-digit drive lines that sink current from the display common cathode. The MAX7219 pulls the digit outputs to V+ when turned off. The MAX7221's digit drivers are high-impedance when turned off.                                                 |

| 4, 9                 | GND                | Ground. Both GND pins must be connected.                                                                                                                                                                                                              |

| 12                   | LOAD<br>(MAX7219)  | Load-Data Input. The last 16 bits of serial data are latched on LOAD's rising edge.                                                                                                                                                                   |

| 12                   | CS<br>(MAX7221)    | Chip-Select Input. Serial data is loaded into the shift register while $\overline{CS}$ is low. The last 16 bits of serial data are latched on $\overline{CS}$ 's rising edge.                                                                         |

| 13                   | CLK                | Serial-Clock Input. 10MHz maximum rate. On CLK's rising edge, data is shifted into the internal shift register. On CLK's falling edge, data is clocked out of DOUT. On the MAX7221, the CLK input is active only while $\overline{\text{CS}}$ is low. |

| 14–17,<br>20–23      | SEG A-SEG G,<br>DP | Seven Segment Drives and Decimal Point Drive that source current to the display. On the MAX7219, when a segment driver is turned off it is pulled to GND. The MAX7221 segment drivers are high-impedance when turned off.                             |

| 18                   | ISET               | Connect to $V_{DD}$ through a resistor (R <sub>SET</sub> ) to set the peak segment current (Refer to Selecting R <sub>SET</sub> Resistor and Using External Drivers section).                                                                         |

| 19                   | V+                 | Positive Supply Voltage. Connect to +5V.                                                                                                                                                                                                              |

| 24                   | DOUT               | Serial-Data Output. The data into DIN is valid at DOUT 16.5 clock cycles later. This pin is used to daisy-chain several MAX7219/MAX7221's and is never high-impedance.                                                                                |

Data is sent in 16-bit packet. Each bit is shifted (into DIN) at the rising edge of the CLK. Data is latched on the rising edge of the LOAD/CS pin. LOAD/CS must go high concurrently or after 16th rising CLK edge but before the 17th rising CLK edge.

|  | D15 | D14 | D13 | D12 | D11 | D10    | D9      | D8       | D7    | D6      | D5  | D4 | D3 | D2  | D1 | D0 |

|--|-----|-----|-----|-----|-----|--------|---------|----------|-------|---------|-----|----|----|-----|----|----|

|  | Х   | Х   | Х   | Х   |     | ADDF   | RESS    |          | MSB   |         |     | DA |    | LSB |    |    |

|  |     |     |     |     |     | Figure | 14 Seri | ial-Data | Forma | t MAX7. | 219 |    |    |     |    |    |

**ADDRESS** HEX REGISTER D15-CODE D11 D10 D9 D8 D12 No-Op Χ 0 0 0 0xX0 Digit 0 Χ 0 0 0 1 0xX1 Digit 1 Х 0 0 1 0 0xX2 Digit 2 Χ 0 0 1 1 0xX3 Digit 3 Χ 0 0xX4 0 1 0 Digit 4 Χ 1 0 1 0xX5 Χ Digit 5 0 1 1 0 0xX6 Digit 6 Х 0 1 1 1 0xX7 Digit 7 Χ 1 0 0 0 0xX8 Decode Χ 1 0 0 1 0xX9 Mode Intensity Χ 1 0xXA Scan Limit Χ 1 0 1 1 0xXB Shutdown Х 0 1 1 0 0xXC Display Χ 0xXF 1 1 Test

Figure 15 MAX7219 Register Address Map

MAX7219 consists of 14 addressable digit and control registers. Digit register which ranges from 0x00 to 0x08 can be used to configure and update individual digit displays. Control Registers range from 0x09 till 0x0F. It consists of Decode Mode Register<0x09> which sets BCD code B or no-decode operation. If decode mode is enabled, the decoder checks the lower nibble of the data in the digit register (D3 – D0) and D7 is used for setting the Decimal Point. If no decode format is selected, data bits D7 – D0 corresponds to the segment lines.

| DECODE MODE                                              | REGISTER DATA |    |    |    |    |    |    |    |      |

|----------------------------------------------------------|---------------|----|----|----|----|----|----|----|------|

| DECODE MODE                                              | D7            | D6 | D5 | D4 | D3 | D2 | D1 | D0 | CODE |

| No decode for digits 7–0                                 | 0             | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0x00 |

| Code B decode for digit 0<br>No decode for digits 7–1    | 0             | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0x01 |

| Code B decode for digits 3–0<br>No decode for digits 7–4 | 0             | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 0x0F |

| Code B decode for digits 7-0                             | 1             | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0xFF |

Figure 16 Decode-Mode Register Example MAX7219

| 7-SEGMENT |     | RE    |    | ON SEGMENTS = 1 |    |    |     |   |   |   |   |   |   |   |

|-----------|-----|-------|----|-----------------|----|----|-----|---|---|---|---|---|---|---|

| CHARACTER | D7* | D6-D4 | D3 | D2              | D1 | D0 | DP* | Α | В | С | D | Е | F | G |

| 0         |     | Х     | 0  | 0               | 0  | 0  |     | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1         |     | Х     | 0  | 0               | 0  | 1  |     | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 2         |     | Х     | 0  | 0               | 1  | 0  |     | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 3         |     | Х     | 0  | 0               | 1  | 1  |     | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 4         |     | Х     | 0  | 1               | 0  | 0  |     | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 5         |     | Х     | 0  | 1               | 0  | 1  |     | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 6         |     | Х     | 0  | 1               | 1  | 0  |     | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 7         |     | Х     | 0  | 1               | 1  | 1  |     | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 8         |     | Х     | 1  | 0               | 0  | 0  |     | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 9         |     | Х     | 1  | 0               | 0  | 1  |     | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| _         |     | Х     | 1  | 0               | 1  | 0  |     | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| E         |     | Х     | 1  | 0               | 1  | 1  |     | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| Н         |     | Х     | 1  | 1               | 0  | 0  |     | 0 | 1 | 1 | 0 | 1 | 1 | 1 |

| L         |     | Х     | 1  | 1               | 0  | 1  |     | 0 | 0 | 0 | 1 | 1 | 1 | 0 |

| Р         |     | Х     | 1  | 1               | 1  | 0  |     | 1 | 1 | 0 | 0 | 1 | 1 | 1 |

| blank     |     | X     | 1  | 1               | 1  | 1  |     | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

<sup>\*</sup>The decimal point is set by bit D7 = 1

Figure 17 Code B Format MAX7219

Shutdown Register <0x0C> is used to set the driver in Shutdown more or Normal Operation Mode. Setting the D0 bit as 1 makes the driver work in Normal Operation. In Shutdown mode the MAX7219 oscillator is halted and all displays are pulled to V+ which blanks the displays. Maximum current consumption in shutdown mode is  $150\mu$ A. It takes  $250\mu$ S for MAX7219 to leave the shutdown mode and enter the normal operation mode. Intensity can be controlled by using the Intensity Control Register <0x0A>. Initially the intensity is set by RSET resistor connected between V+ and ISET and the minimum value should be  $9.53k\Omega$  which sets the segment current at 40mA. For further control of the brightness Intensity Control register is used. The MAX7219 has an internal pulse-width modulator which is controlled by lower nibble of intensity register. The intensity value ranges from 0x00 (Min brightness) – 0x0F (Max brightness). Another important control register is the Scan-Limit Register <0x0B>. Scan limit sets how many digits are displayed from 1 to 8. As the digits are displayed in multiplexed manner with typical scan rate of 800Hz with 8 digits, if fewer digits are displayed the scan rate is 8Fosc/N where N is the number of digits scanned. On Initial Power-Up all the control registers are Reset, the display is blanked, display scan is one digit and the driver is in shutdown mode.

To minimize power supply ripple, a  $10\mu F$  electrolytic capacitor and a  $0.1\mu F$  ceramic capacitor is to be connected between the V+ and GND as close to device as possible. For calculation of RSET and Power Dissipation calculation refer Page 33 MAX7219 Electrical Characteristics.

### 2.2.2 Interfacing MAX7219 with PIC16F887 using SPI protocol

PIC16F887 consist of Master Synchronous Serial Port (MSSP) module which can be used for Serial communication with other devices. MSSP can be operated in SPI or I2C mode. For interfacing with MAX7219 display driver SPI protocol is used. For using MSSP SSPSTAT, SSPCON & SSPCON2 registers are used. SPI mode supports 8 bits of data to be synchronously transmitted and received. For communication with MAX7219 4 pins are used:

- Serial Data Out (SDO) RC5

- Serial Data In (SDI) RC4

- Serial Clock (SCK) RC3

- Latching the Data (SS) RD0

In order to configure MSSP in SPI mode, SSPCON and SSPSTAT bits have to be programmed. For interfacing with MAX7219, PIC16F887 is used in Master Mode. MSSP has a transmit/receive shift register SSPSR and a buffer register SSPBUF. SSPSR shifts the data out (MSB first). SSPSR is not directly readable or writable and can only be addressed through SSPBUF. In order to configure MSSP in SPI mode, SSPEN bit in SSPCON must be set. Default mode of MSSP on reset is SPI Master Mode with CLK = Fosc/4. The corresponding SDI pin is automatically controlled by MSSP while SDO pin has to be configured as an input by clearing the TRISC bit. SCK pin must have TRISC bit as set. For the project SS pin is not utilized so it is disabled by clearing the corresponding TRISC bit and is configured as LOAD pin for MAX7219.

| R/W-0 | R/W-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| SMP   | CKE   | D/Ā | Р   | s   | R/W | UA  | BF    |

| bit 7 |       |     |     |     |     |     | bit 0 |

| Legend:           |                  |                                  |                    |  |

|-------------------|------------------|----------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as ' | 0,                 |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared             | x = Bit is unknown |  |

#### bit 7 SMP: Sample bit

SPI Master mode: 1 = Input data sampled at end of data output time

0 = Input data sampled at middle of data output time

SPI Slave mode: SMP must be cleared when SPI is used in Slave mode

#### In I2C Master or Slave mode:

Slew rate control disabled for standard speed mode (100 kHz and 1 MHz)

0 = Slew rate control enabled for high speed mode (400 kHz)

#### bit 6 CKE: SPI Clock Edge Select bit

CKP = 0: 1 = Data transmitted on rising edge of SCK 0 = Data transmitted on falling edge of SCK

#### CKP = 1:

1 = Data transmitted on falling edge of SCK

#### 0 = Data transmitted on rising edge of SCK

D/A: Data/Address bit (I2C mode only) bit 5

1 = Indicates that the last byte received or transmitted was data

0 = Indicates that the last byte received or transmitted was address

#### bit 4 P: Stop bit

(I<sup>2</sup>C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.)

1 = Indicates that a Stop bit has been detected last (this bit is '0' on Reset)

0 = Stop bit was not detected last

(I<sup>2</sup>C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.)

1 = Indicates that a Start bit has been detected last (this bit is '0' on Reset)

0 = Start bit was not detected last

#### R/W: Read/Write bit information (I2C mode only) bit 2

This bit holds the RW bit information following the last address match. This bit is only valid from the address match to the next Start bit, Stop bit, or not ACK bit.

In I2C Slave mode:

0 = Write

#### In I2C Master mode:

Transmit is in progress 0 = Transmit is not in progress

OR-ing this bit with SEN, RSEN, PEN, RCEN, or ACKEN will indicate if the MSSP is in Idle mode.

#### UA: Update Address bit (10-bit I2C mode only)

1 = Indicates that the user needs to update the address in the SSPADD register

0 = Address does not need to be updated

#### BF: Buffer Full Status bit bit 0

Receive (SPI and I<sup>2</sup>C modes): 1 = Receive complete, SSPBUF is full

0 = Receive not complete, SSPBUF is empty

#### Transmit (I<sup>2</sup>C mode only):

1 = Data transmit in progress (does not include the  $\overline{ACK}$  and Stop bits), SSPBUF is full 0 = Data transmit complete (does not include the  $\overline{ACK}$  and Stop bits), SSPBUF is empty

Figure 19 SSPSTAT SSP Status Register

| R/W-0             | R/W-0                                                                                                                                                                                                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                                                             | R/W-0                                                                               | R/W-0                                                                             | R/W-0                                 | R/W-0                                     |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------|

| WCOL              | SSPOV                                                                                                                                                                                                                                                                                                                                                  | SSPEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CKP                                                                                                                               | SSPM3                                                                               | SSPM2                                                                             | SSPM1                                 | SSPM0                                     |

| bit 7             |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                   |                                                                                     |                                                                                   |                                       | bit 0                                     |

|                   |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                   |                                                                                     |                                                                                   |                                       |                                           |

| Legend:           |                                                                                                                                                                                                                                                                                                                                                        | W = Writable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                   | II – Unimalama                                                                      | ented bit, read as '0                                                             | v                                     |                                           |

| R = Readable bit  |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                   |                                                                                     |                                                                                   |                                       |                                           |

| -n = Value at POR | <u> </u>                                                                                                                                                                                                                                                                                                                                               | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                   | '0' = Bit is clear                                                                  | ed                                                                                | x = Bit is unknow                     | wn                                        |

| bit 7             | Master mode:  1 = A write to to to to e. No collision Slave mode:                                                                                                                                                                                                                                                                                      | n<br>JF register is writter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •                                                                                                                                 |                                                                                     | inditions were not vious word (must be d                                          |                                       |                                           |

| bit 6             | In SPI mode:  1 = A new byte is lost. Ove data, to avo initiated by 0 = No overflor In I <sup>2</sup> C mode: 1 = A byte is re                                                                                                                                                                                                                         | rflow can only occupid setting overflow, writing to the SSPE w eceived while the State of the St | e SSPBUF regis<br>r in Slave mode.<br>In Master mode<br>BUF register (mu                                                          | In Slave mode, the<br>the overflow bit is<br>to be cleared in so                    | he previous data. In<br>the user must read the<br>not set since each<br>oftware). | e SSPBUF, even i<br>new reception (an | f only transmitting<br>d transmission) is |

| bit 5             | In both modes, vin SPI mode:  1 = Enables se 0 = Disables si In I <sup>2</sup> C mode: 1 = Enables the                                                                                                                                                                                                                                                 | rial port and config<br>erial port and confi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | se pins must be<br>ures SCK, SDO,<br>igures these pin<br>nfigures the SDA                                                         | SDI and SS as th<br>s as I/O port pins<br>and SCL pins as                           | the source of the se                                                              | al port pins                          |                                           |

| bit 4             | 0 = Idle state for<br>In I <sup>2</sup> C Slave mo<br>SCK release con<br>1 = Enable clock                                                                                                                                                                                                                                                              | clock is a high lever clock is a low lever de:  other clock is a low lever de:  other clock stretch ode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | el                                                                                                                                | e data setup time                                                                   | ž.)                                                                               |                                       |                                           |

| bit 3-0           | 0000 = SPI Mas<br>0001 = SPI Mas<br>0010 = SPI Mas<br>0011 = SPI SIav<br>0100 = SPI SIav<br>0101 = SPI SIav<br>0110 = I <sup>2</sup> C SIav<br>0110 = I <sup>2</sup> C SIav<br>1000 = I <sup>2</sup> C Mas<br>1001 = Load Mi<br>1010 = Reserve<br>1011 = I <sup>2</sup> C Sirv<br>1101 = Reserve<br>1101 = Reserve<br>1110 = Reserve<br>1110 = Reserve | e mode, 7-bit addi<br>e mode, 10-bit addi<br>ter mode, clock =<br>ask function<br>ad<br>ware controlled Ma<br>d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Fosc/4 Fosc/16 Fosc/64 TMR2 output/2 CK pin, SS pin CK pin, SS pin cess dress Fosc / (4 * (SSF aster mode (Slav ress with Start a | control enabled<br>control disabled,<br>PADD+1})<br>re idle)<br>and Stop bit intern |                                                                                   | s I/O pin                             |                                           |

|                   |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                   | SPCON Regis                                                                         |                                                                                   |                                       |                                           |

|                   |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | H10111P /11 S                                                                                                                     | ALLIN ROOM                                                                          | ter                                                                               |                                       |                                           |

In MAX7219, data is latched on the rising edge of the LOAD/CS pin. So PIC16F887 PORTA Pin 5 is connected to LOAD/CS pin in MAX7219 for latching the data once all the packet is transferred. In MAX7219, as the data is moved in during the rising edge of the CLK, in the SSPSTAT CKE bit is set to make the data transmission during the rising edge of CLK. CKP is default 0 which makes sure the default level of CLK is 0V. BF bit (Buffer Full) is polled in the SSPSTAT register of PIC16F887 to ensure the data transmission is complete before the new data is sent.

#### MAX7219 and PIC16F887 SPI Function Snippet

```

Code Snippet 1 SPI data transfer function (to MAX7219)

/*

SPI communication between PIC16F887 and MAX7219

Call SPI_tx(addr,data) with Address of the register and the corresponding data to be sent.

*/

void SPI_tx(unsigned char addr,unsigned char dat)

{

PORTA.F5 = 0;//LOAD_CS pin is made low

SSPBUF = addr;//Send the address first