#

CR16C Programmer's Reference Manual

Part Number: 424521772-101

March 2002

# **REVISION RECORD**

| VERSION | RELEASE DATE  | SUMMARY OF CHANGES                                                  |

|---------|---------------|---------------------------------------------------------------------|

| 1.0     | December 2000 | First release.                                                      |

| 1.1     | February 2001 | Changed BAL/Bcond to ±16 MByte.<br>Minor clarificatons/corrections. |

| 3.1     | March 2002    | Product release for CR16B/C.                                        |

## PREFACE

This Programmer's Reference Manual presents the programming model for the CompactRISC CR16C microprocessor core. The key to system programming, and a full understanding of the characteristics and capabilities of the CompactRISC<sup>TM</sup> Toolset, is understanding the programming model.

The information contained in this manual is for reference only and is subject to change without notice.

No part of this document may be reproduced in any form or by any means without the prior written consent of National Semiconductor Corporation.

National Semiconductor is a registered trademark and CompactRISC is a trademark of National Semiconductor Corporation. All other brand or product names are trademarks or registered trademarks of their respective holders

This page is intentionally blank.

#### Chapter 1 INTRODUCTION

| 1.1       | NATIONAL'S COMPACTRISC TECHNOLOGY          | -1 |

|-----------|--------------------------------------------|----|

| 1.2       | CR16C 16-BIT COMPACTRISC PROCESSOR CORE    | -1 |

| 1.3       | THE COMPACTRISC ARCHITECTURE1              | -2 |

| 1.4       | REDUCED MEMORY REQUIREMENTS1               | -3 |

| 1.5       | SCALABLE ARCHITECTURE FROM 8 TO 64 BITS 1- | -4 |

| 1.6       | MODULAR EXTENSIONS1                        | -4 |

| 1.7       | DEVELOPMENT TOOLS1                         | -5 |

|           |                                            |    |

| Chapter 2 | PROGRAMMING MODEL                          |    |

| 2.1       | COMPATIBILITY WITH CR16A AND CR16B24       | -1 |

| 2.2 | DATA  | TYPES                         | 2-1  |

|-----|-------|-------------------------------|------|

| 2.3 | REGI  | STER SET                      | 2-2  |

|     | 2.3.1 | General-Purpose Registers     | 2-3  |

|     | 2.3.2 | Dedicated Address Registers   | 2-3  |

|     | 2.3.3 | The Processor Status Register | 2-4  |

|     | 2.3.4 | The Configuration Register    | 2-6  |

| 2.4 | INSTF | RUCTION SET                   | 2-8  |

| 2.5 | MEMO  | DRY ORGANIZATION              | 2-12 |

|     | 2.5.1 | Data References               | 2-13 |

|     | 2.5.2 | Stacks                        | 2-14 |

| 2.6 | ADDR  | ESSING MODES                  | 2-15 |

## Chapter 3 EXCEPTIONS

| 3.1 | INTRO | DDUCTION                   | 3-1 |

|-----|-------|----------------------------|-----|

| 3.2 | INTEF | RRUPT HANDLING             | 3-2 |

| 3.3 | TRAP  | S                          | 3-3 |

| 3.4 | DETA  | ILED EXCEPTION PROCESSING  | 3-4 |

|     | 3.4.1 | Instruction Endings        | 3-4 |

|     | 3.4.2 | The Dispatch Table         | 3-5 |

|     | 3.4.3 | Acknowledging an Exception | 3-6 |

|     | 3.4.4 | Exception Service Procedures                | 3-9    |

|-----|-------|---------------------------------------------|--------|

|     | 3.4.5 | Returning from Exception Service Procedures | 3-9    |

|     | 3.4.6 | Priority Among Exceptions                   | . 3-10 |

|     | 3.4.7 | Nested Interrupts                           | . 3-12 |

| 3.5 | RESE  | Т                                           | . 3-13 |

#### Chapter 4 ADDITIONAL TOPICS

| 4.1       | DEBU  | GGING SUPPORT                                   | 4-1  |

|-----------|-------|-------------------------------------------------|------|

|           | 4.1.1 | Instruction Tracing                             | 4-1  |

|           | 4.1.2 | The Breakpoint Instruction                      |      |

|           | 4.1.3 | User Programmable Breakpoint Features           |      |

|           | 4.1.4 | Example Breakpoints                             |      |

|           | 4.1.5 | In-System Emulator (ISE)                        |      |

|           | 4.1.6 | Hardware Debug Mode                             |      |

|           | 4.1.7 | Debug Control and Status Registers              |      |

| 4.2       | CACH  | E SUPPORT                                       |      |

|           | 4.2.1 | Instruction Cache Operation                     |      |

|           | 4.2.2 | Instruction Cache Invalidation                  |      |

|           | 4.2.3 | Data Cache Operation                            |      |

|           | 4.2.4 | Data Write Operation                            |      |

|           | 4.2.5 | Data Cache Invalidation and Coherence Support . |      |

|           | 4.2.6 | Data Cache Monitoring                           |      |

| 4.3       | INSTR | RUCTION EXECUTION ORDER                         | 4-24 |

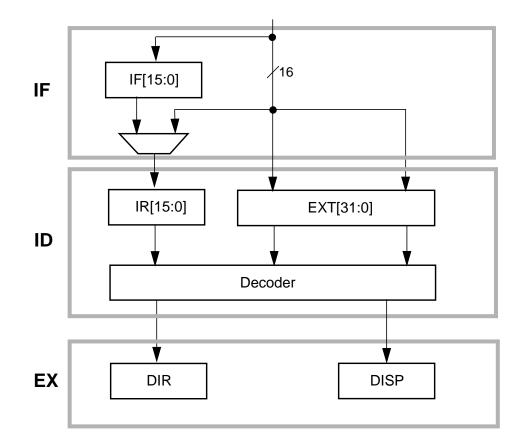

|           | 4.3.1 | The Instruction Pipeline                        |      |

|           | 4.3.2 | Serializing Operations                          |      |

| Chapter 5 | INS   | STRUCTION SET                                   |      |

| 5.1       | INSTR | RUCTION DEFINITIONS                             | 5-1  |

- Appendix A INSTRUCTION EXECUTION TIMING

- Appendix B INSTRUCTION SET ENCODING

- Appendix C STANDARD CALLING CONVENTIONS

- Appendix D COMPARING CR16C WITH CR16A/B

- INDEX

## 1.1 NATIONAL'S CompactRISC TECHNOLOGY

National Semiconductor's CompactRISC architecture was created from the ground up as an alternative solution to CISC and other accumulator based architectures. The CompactRISC architecture is a RISC architecture specifically designed for embedded systems. It features the best of RISC and CISC with compact code generation, low power consumption, silicon-efficient implementations, the ability to tightly integrate on-chip acceleration, I/O and memory functions, and scalability from 8 to 64 bits.

CompactRISC implementations greatly reduce the amount of silicon required for the CPU, code memory and data memory, without significantly reducing the overall performance advantages of RISC. In addition, because any processing core is only as good as its peripheral support, several key architectural decisions were made to optimize bus structures and I/O control for embedded systems in order to improve flexibility and reduce costs.

Since its introduction, the CompactRISC architecture has firmly established itself by filling a market gap: those embedded applications that require the performance of RISC, but cannot afford the processing and cost overheads of 32-bit RISC implementations. The 16-bit members of the CompactRISC family have been particularly popular with designers because of their optimal balance of cost and performance, plus the ability to combine a very small size core with other key on-chip functions.

## 1.2 CR16C 16-BIT CompactRISC PROCESSOR CORE

The CR16C is a third-generation 16-bit CompactRISC processor core. It is assembly-level compatible with its predecessors, the CompactRISC CR16A and CR16B, and provides expanded options for system designers. The new implementation provides:

- 1. Address Space

- Expanded linear address space of 16 Mbytes for program code and data memory

- User, supervisor and interrupt stack pointers covering the full address range

- 2. Instruction Set Enhancements

- Double-word support for most instructions improve optimizations for data and code access above the first 64K.

- load and store

- move and movex/z  $\,$

- arithmetic (compare, add, subtract)

- logic (AND, OR, XOR)

- shifts (arithmetic and logical)

- Expanded push/pop instructions allow up to eight registers with a separate bit to determine if the return address should also be pushed/popped to/from the stack

- expanded load/store multiple instructions to allow up to 8 registers.

- optional mac instruction

- 3. Addressing Modes Enhancements

- Index addressing mode for better support of relocatable code

- Register pair relative addressing mode, with efficient instruction encoding for all memory access instructions, improves optimizations for data and code access above the first 64K.

- 4. System Features

- User/supervisor mode

- Illegal address trap (address out of range)

- Cache support

- Enhanced debug features, with up to eight hardware breakpoints

- 5. Speed Improvements

- Enhanced pipelining of data transfers

- Faster/deterministic multiply (single cycle 8\*8)

To ensure a seamless transition for existing CompactRISC users, the CR16C provides a configuration bit, CFG.SR, that permits exclusive use of only small registers. This mode is backward compatible with the large programing model of the CR16B. The small programing model of the CR16B, which is backward compatible with the CR16A, is no longer supported.

#### **1.3 THE COMPACTRISC ARCHITECTURE**

In many ways, the CompactRISC architecture is a traditional RISC load/store processor architecture, but enhanced for embedded control functions.

For example:

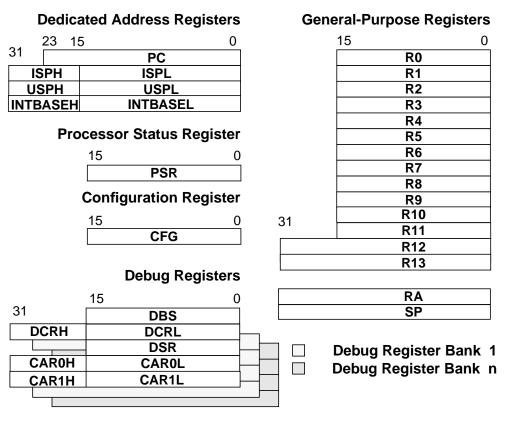

- The CR16C executes an optimized instruction set with up to 33 internal registers grouped in 16 general-purpose registers, four dedicated address registers, a processor status register, a configuration register and up to 11 debug-control registers.

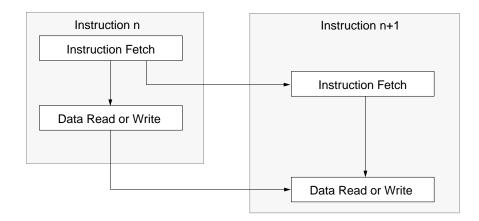

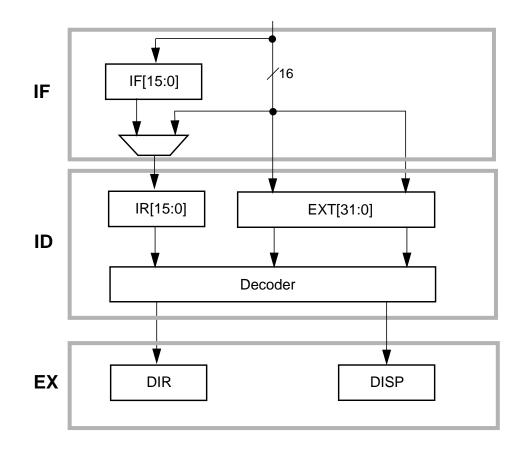

- The CR16C has a three-stage pipeline that is used to obtain a peak performance of 50 Million Instructions Per Second (MIPS) at a clock frequency of 50 MHz.

- The CR16C core includes a pipelined integer unit that supports a peak execution speed of one instruction per each internal cycle, with a 100 Mbyte/sec pipelined bus.

- The CR16C performs fast multiply operations using a 16-bit by 8-bit hardware multiplier.

In general, the CompactRISC architecture supports little-endian memory addressing. This means that the byte order in the CR16C is from the least significant byte (LSB) to the most significant byte (MSB).

#### 1.4 REDUCED MEMORY REQUIREMENTS

To simplify instruction decoder design, RISC architectures have traditionally employed fixed-width instructions. For 32-bit RISC systems, every instruction is encoded in four or eight bytes. In CISC systems, a variable instruction length is used, resulting in smaller code sizes for a given application. The CompactRISC architecture utilizes variable instruction widths with fixed coding fields within the instruction itself. For example, the opcode field is always in the first 16 bits, with additional bytes as required for immediate values. Instructions for the CR16C may be encoded in 2, 4 or 6 bytes, but basic instructions are only 2 bytes long. This permits optimized instruction processing by the instruction decoder, and results in a smaller code size. Code generated for the CR16C is comparable to CISC code size, or typically 50 percent smaller than code generated for leading 32-bit RISC CPUs. Another advantage is the ability to generate performance with lower pin-counts or lower bandwidth buses, again a trait of an embedded system.

32-bit RISC processors store registers and addresses on the stack as 32bit entities. The CR16C is a 16-bit processor, thus it uses 16 bits for register image storage and for address storage in main memory. In addition, 32-bit RISC processors deliver high performance only when aligned 32bit data is used. Non-aligned data significantly hampers performance. Intermediate results are stored in memory as 32-bit values and registers are saved as 32-bit operands on the stack. CompactRISC instructions operate on 8-, 16- and 32-bit data. Non-aligned accesses are allowed. Dedicated data type conversion instructions speed data access to mixed size data. With smaller code size and variable length instructions and data, the CompactRISC family provides more efficient use of smaller, lower cost, lower bandwidth memories.

Smaller memory enables the designer to choose between several potential advantages:

- Reduced costs

- Many more system elements integrated with on-chip memory

- Fewer pins to access minimum-sized off-chip memory

- Larger amounts of on-chip memory than similar processors, at the same cost.

#### 1.5 SCALABLE ARCHITECTURE FROM 8 TO 64 BITS

The architectural features described above make the CompactRISC technology ideal for the next generation of embedded systems. One additional design decision opened the door for CompactRISC technology to be effectively used from low-end to high-end embedded systems: the Compact-RISC architecture is flexible enough to accommodate the whole range of 8-bit to 64-bit implementations, thus providing a more attractive upgrade path for designers of new, low-end embedded systems.

Thus, the designer of embedded controller-based systems can choose the optimum processor size for a given target application. This is particularly useful in leveraging the development investment across several classes of related end products. With a single-processor architecture, a number of different products can be developed using a single development platform and using the same HLL-based development and debug tools. Additionally, a design team that is already experienced with a design using one CompactRISC core can easily migrate to another core, due to the high similarity in both the architecture and the development tools.

#### 1.6 MODULAR EXTENSIONS

The CompactRISC technology was designed to be easily extended. This means that specialized functions needed by specific applications can be easily added to a single-chip design. A modular internal bus provides predefined processor and I/O interfaces to the core bus and the peripheral bus. These buses are designed for maximum flexibility. The core bus is a high-speed bus and can be used to connect performance-demanding functions to the CPU such as fast on-chip memory, DMA channels, and

additional coprocessor units such as a DSP. The peripheral bus is a simple, lower speed bus for less demanding peripherals such as counters, timers, PWM lines and MICROWIRE serial interfaces. Using a "template" approach, it is easy to create small, cost-effective custom systems. It is also easy to expand the functionality of CompactRISC core-based systems to include any number of application specific features.

## 1.7 DEVELOPMENT TOOLS

High-level development tools are essential to rapid, modern design. The CompactRISC architecture is well supported with a comprehensive C-based development and debug environment available from National and third party vendors. Key software development components include an optimizing C compiler, a macro assembler, run-time libraries, librarian and a graphical source-level debugger with enhanced simulation capabilities. In addition, an integrated, multiple core, graphical debugger supports debugging of multiple CompactRISC/DSP cores on a single die.

On the hardware side, the CompactRISC architecture has modular ISE (In System Emulator) support from third-party development system vendors, and various development boards for all current product offerings.

The CR16C supports a NEXUS class 1 compliant on-chip debug module. With this interface, every debugger that uses the industry standard NEXUS API can be used for CR16C-based System-on-a-Chip (SOC) designs.

The CompactRISC architecture is also well supported with Real-Time Operating Systems (RTOS) from third party vendors.

As a package, these tools simplify the task of designing and developing advanced embedded systems in high level languages such as ANSI-C.

This page is intentionally blank.

# Chapter 2 PROGRAMMING MODEL

This chapter describes the CR16C register set and the instruction set. The CR16C supports up to 16 Mbytes of program and data space. Five addressing modes are supported: register, immediate, absolute, relative and indexed. Refer to Section 2.5 for an overview of the memory areas with most efficient data accesses.

## 2.1 COMPATIBILITY WITH CR16A AND CR16B

The CR16C is backward-compatible with the CR16A and CR16B. The CR16C maintains assembly level compatibility, not binary compatibility, with the CR16B large model. Code that was developed for the CR16B large model runs on the CR16C after being reassembled for the CR16C. Appendix D provides a summary of the differences between the CR16A/B and the CR16C programming models.

#### 2.2 DATA TYPES

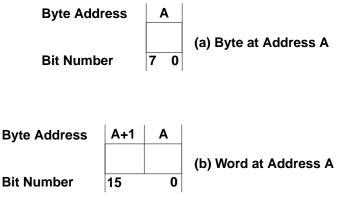

The CompactRISC family of processors are little-endian machines. As such, the LSB always resides in the lower address, both for address and data variables.

- **Integer data type**The integer data type is used to represent integers. Integers may be signed or unsigned. Three integer sizes are supported: 8-bit (1 byte), 16bit (1 word) and 32-bit (1 double-word). Signed integers are represented as binary 2's complement numbers, with values in the range  $-2^7$  to  $2^7$ -1,  $-2^{15}$  to  $2^{15}$ -1 and  $-2^{31}$  to  $2^{31}$ -1, respectively. Unsigned numbers have values in the range 0 to  $2^8$ -1, 0 to  $2^{16}$ -1 and 0 to  $2^{32}$ -1, respectively.

- **Boolean data type** The Boolean data type is represented as an integer (either a byte or a word). The value of its least significant bit represents one of two logical values: true (integer 1) or false (integer 0). Bits other than the least significant bit are not interpreted.

## 2.3 REGISTER SET

This section describes the register set of the CR16C. The format of each register is illustrated and described in detail. Bits/Registers specified as "reserved" must be written as 0, and return undefined results when read. Non-implemented registers are read as zero.

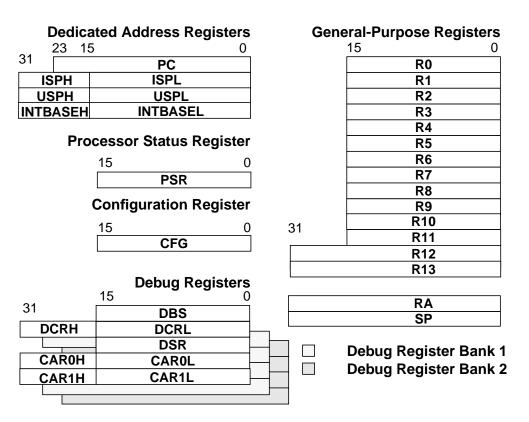

The internal registers of the CR16C are grouped by function:

- 16 general-purpose registers including four double registers:

- Two available for use in index addressing mode

- One used as a return address pointer

- One used as the stack pointer

- Four dedicated address registers

- One Processor Status Register

- One Configuration Register

- Five debug registers supporting two debug channels.

- Optionally, additional sets of four debug registers for each pair of auxiliary debug channels.

| Figure 2-1 s | shows the | internal | registers | of the | CR16C. |

|--------------|-----------|----------|-----------|--------|--------|

|              |           |          |           |        |        |

The number of debug registers depends on the configuration of the chip

Figure 2-1. CR16C Internal Registers

## 2.3.1 General-Purpose Registers

The CompactRISC cores feature 16 general-purpose registers. These registers are used individually as 16-bit operands or as register pairs for operations with 32-bit operands or on addresses greater than 16 bits.

- Registers are defined as R0 through R13, RA and SP.

- Register pairs are defined based on the setting of the Short Register bit in the Configuration Register (CFG.SR). When CFG.SR is set, register pairs are defined as in the CR16A/B: (R1,R0), (R2,R1) ... (R11,R10), (R12\_L, R11), (R13\_L, R12\_L), (R14\_L, R13\_L) and SP. (R14\_L, R13\_L) is the same as (RA,ERA).

- When CFG.SR is not set, register pairs are defined as follows: (R1,R0), (R2,R1) ... (R11,R10), (R12\_L, R11), R12, R13, RA, SP.

R12, R13, RA and SP are double-word registers for direct storage of addresses greater than 16 bits.

With the recommended calling convention for the architecture, some of these registers are assigned special hardware and software functions. Registers R0 to R13 are used for general purposes, such as holding variables, addresses or index values. The SP Register is used as a pointer to the program run-time stack. The RA Register is used as a return address from subroutines. R12 and R13 are available for use as a base index address in the index addressing mode.

If a general-purpose register is specified by an operation that is 8 bits long, only the lower part of the register is used; the higher part is not referenced, or modified. Similarly, for word operations on register pairs, only the lower register is used. The upper register is not referenced or modified.

#### 2.3.2 Dedicated Address Registers

This section describes the four, double-word wide, dedicated address registers that the CR16C uses to implement specific address functions.

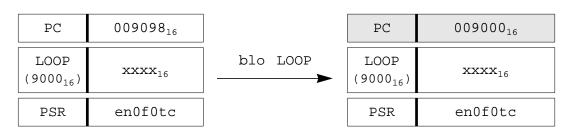

**Program Counter (PC) Register** The value in the PC Register points to the first byte of the instruction currently being executed. CR16C instructions are aligned to even addresses, thus the least significant bit of the PC is always 0. At reset, the PC is initialized to 0 or an alternative predetermined value. The value of the PC prior to reset is saved in the (R1,R0) general-purpose register pair.

| Interrupt<br>Stack Pointer<br>(ISP)        | The ISP points to the lowest address of the last item stored on the inter-<br>rupt stack. This stack is used by the hardware when interrupts or<br>exceptions occur. This stack pointer is accessible as the ISP Processor<br>Register for initialization. The interrupt stack can exist in the entire<br>address range. The ISP cannot be used for any purpose other than the<br>automatic storage of registers on the interrupt stack during an excep-<br>tion, and the restoration of these registers during a RETX. The interrupt<br>stack grows downward in memory. See Section for additional details.<br>The most significant 8 bits of ISP and the least significant bit of ISP are<br>forced to 0. |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| User Stack<br>Pointer (USP)                | The USP points to the lowest address of the last item stored on the user stack. This stack is used when the program stack is used for supervisor and user level processes. This stack also grows downward in memory. See "The program stack" on page 2-14 for more information. If the USP points to an illegal address (any address greater than 0x00FF_FFFF) the execution of a stack modifying instruction (PUSH or POP) an IAD trap.                                                                                                                                                                                                                                                                    |

| Interrupt<br>Base<br>(INTBASE)<br>Register | The INTBASE Register holds the address of the dispatch table for inter-<br>rupts and traps. The dispatch table can be located anywhere in the<br>supported addresses range. The most significant 8 bits of INTBASE and<br>the least significant bit of INTBASE are forced to 0. See Chapter 3 for<br>more information.                                                                                                                                                                                                                                                                                                                                                                                      |

#### 2.3.3 The Processor Status Register

The 16-bit wide Processor Status Register (PSR) holds status information and selects operating modes for the CR16C. See Figure 2-2 for the PSR bit assignment.

| 15     | 12 | 11 | 10 | 9 | 8   | 7 | 6 | 5 | 4   | 3 | 2 | 1 | 0 |

|--------|----|----|----|---|-----|---|---|---|-----|---|---|---|---|

| reserv | ed | I  | Р  | Е | res | Ν | Z | F | res | U | L | Т | С |

#### Figure 2-2. PSR Register

At reset, bits 0 through 11 of the PSR are cleared to 0, except for the PSR.E bit, which is set to 1. In addition, the value of each bit prior to reset is saved in the R2 general-purpose register.

Bits Z, C, L, N, and F in the PSR have a dedicated condition code in conditional branch instructions. Any conditional branch instruction can cause a branch in program execution, based on the value of one or more of these PSR bits. For example, one of the Bcond instructions, BEQ (Branch EQual), causes a branch if the PSR.Z flag is set. Refer to the Bcond instruction in Section 5.1 on page 5-1 for details. Bits 4 and 8 have a constant value of 0. Bits 12 through 15 of the PSR are reserved. The other bits are described below. In general, status bits are modified only by specific instructions. Otherwise, status bits maintain their values throughout instructions which do not implicitly affect them.

- **Bit C** The Carry bit indicates whether a carry or borrow occurred after addition or subtraction. It can be used with the ADDC and SUBC instructions to perform multiple-precision integer arithmetic calculations. It is cleared to 0 if no carry or borrow occurred, and set to 1 if a carry or borrow occurred.

- **Bit T** The Trace bit causes program tracing. When the T bit is set to 1, a Trace (TRC) trap is executed after every instruction. Refer to Section 4.1.1 on page 4-1 for more information on program tracing. The T bit is automatically cleared to 0 when a trap or an interrupt occurs. The T bit is used in conjunction with the P bit (see below). When a hardware debug module is present in the system, the value of the T bit is ignored.

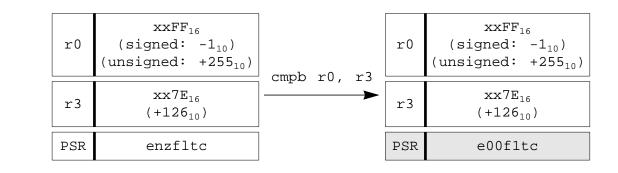

- **Bit L** The Low flag is set by comparison operations. In integer comparison, the L flag is set to 1, if the second operand (*Rdest*) is less than the first operand (*Rsrc*) when both operands are interpreted as unsigned integers. Otherwise, it is cleared to 0. Refer to the specific compare instruction in Section 5.1 on page 5-1 for details.

- **Bit U** The User Mode bit is set to indicate that the User Stack Pointer is being used as the Stack Pointer. This bit can only be set by the Jump USR instruction. This bit is cleared before any exception processing, such as an interrupt or a trap. When this bit is clear, the supervisor stack pointer is used. The USP Register is accessed as a processor register when the User Mode bit is not set. When the User Mode bit is set, Load Processor Register LPR) operations are not permitted. The value of this bit is output on signal SFUSR from the core.

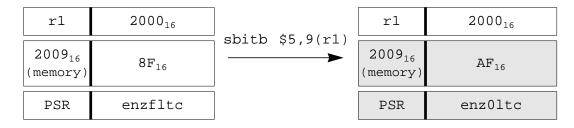

- **Bit F** The Flag bit is a general condition flag which is set by various instructions. It may be used to signal exceptional conditions or to distinguish the results of an instruction (e.g., integer arithmetic instructions use it to indicate overflow from addition or subtraction). It is also set, or cleared, as a result of a Test, Set or Clear bit instruction.

- **Bit Z** The Zero bit is set by comparison operations. In integer comparisons, it is set to 1 if the two operands are equal. Otherwise, it is cleared to 0. Refer to the specific compare instruction in Section 5.1 on page 5-1 for details.

- **Bit N** The Negative bit is set by comparison operations. In integer comparison, it is set to 1 if the second operand (*Rdest*) is less than the first operand (*Rsrc*), when both operands are interpreted as signed integers. Otherwise, it is cleared to 0. Refer to the specific compare instruction in Section 5.1 on page 5-1 for details.

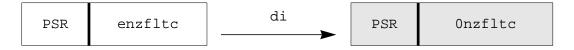

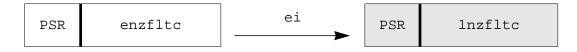

**Bit E** The local maskable interrupt Enable bit affects the state of maskable interrupts. When this bit and the PSR.I bits are 1, all maskable interrupts are accepted. When this bit is 0, only the non-maskable interrupt is accepted. See Section 3.2 on page 3-2.

There are two dedicated instructions that set and clear the E bit: the Enable Interrupts instruction (EI) sets it to 1; the Disable Interrupts instruction (DI) clears it to 0. This pair can be used to locally disable maskable interrupts, regardless of the global state of maskable interrupts which is determined by the value of the PSR.I bit.

See also Section 3.2 on page 3-2.

- **Bit P** The Trace (TRC) trap Pending bit is used together with the T bit to prevent a TRC trap from occurring more than once for any instruction. It is cleared when no TRC trap is pending. It is set when a TRC trap is pending. See Sections 3.4.4 on page 3-9 and 4.1.1 on page 4-1 for more information. When a hardware debug module is present in the system the value of the P bit is ignored.

- **Bit I** The global maskable Interrupt enable bit affects the state of maskable interrupts. This bit is set using the LPR instruction. When this bit and the PSR.E bits are 1, all maskable interrupts are accepted. When this bit is 0, only the non-maskable interrupt is accepted. This bit is cleared to 0 on reset. In addition, it is automatically cleared when an interrupt or DBG trap occurs.

#### 2.3.4 The Configuration Register

The Configuration Register (CFG) is used to enable or disable various operating modes and to control optional on-chip caches.Figure 2-3 shows the CFG Register bit assignment.

| 15-10    | 9  | 8  | 7 | 6 | 5   | 4  | 3   | 2  | 1 | 0 |

|----------|----|----|---|---|-----|----|-----|----|---|---|

| reserved | SR | ED | 0 | 0 | LIC | IC | LDC | DC | 0 | 0 |

#### Figure 2-3. Configuration Register

All CFG bits are cleared on reset. The CFG control bits are described in detail below.

**Bit DC** If the Data Cache bit is set to 1, the data cache is accessible for data read and write operations. If the DC bit is cleared to 0, the data cache is disabled.

- **Bit LDC** If the Lock Data Cache line bit is set to 1, a missing line, which cannot be replaced, is locked into the cache after it is placed. If LDC is cleared to 0, the line can be replaced.

- **Bit IC** If the Instruction Cache bit is set to 1, the instruction cache is accessible for instruction fetches. If the IC bit is cleared to 0, the instruction cache is disabled.

- **Bit LIC** If the Lock Instruction Cache line bit is set to 1, a missing instruction is locked into the instruction cache after it is placed. It is not replaced as long as LIC remains 1.

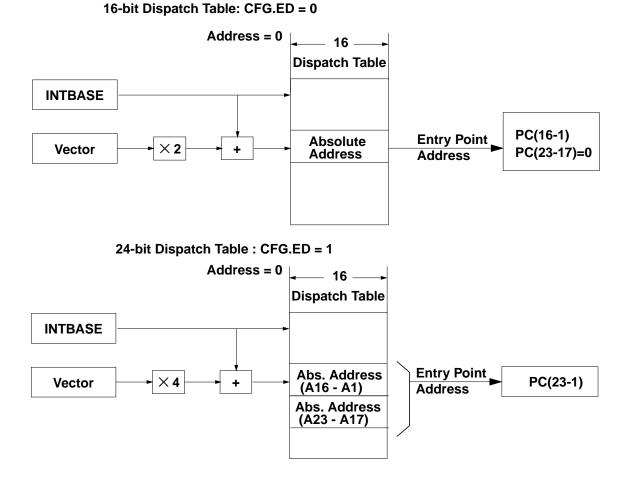

- **Bit ED** The Extended Dispatch bit determines the size of an entry in the Interrupt Dispatch Table. Each entry holds the address of the appropriate exception handler. When ED is set, the Interrupt Dispatch Table contains 32-bit elements, each occupying two adjacent words. When ED is cleared, the Interrupt Dispatch Table contains 16-bit elements. This implies that when ED is clear, all exception handlers must start in the first 128K of the address space. On reset, the bit is cleared. The location of the Interrupt Dispatch Table is determined by INTBASE, independent of the setting of the ED bit.

- **Bit SR** The Short Register bit is set to enable the register pairing used to maintain compatibility with code developed for the CR16B large model. As opposed to using the extended versions of R12, R13 and R14, only the lower 16 bits of these registers are used, and are paired together as register pairs for double operations. The (R14, R13) register pair is used as the extended RA. In addition, when this bit is set, address displacements relative to a single register are supported with offsets of 0 and 14 bits in place of the index addressing with these displacements. See "Index mode" on page 2-16 for additional details.

#### The Debug RegistersDebug Base Register (DBS)

The Debug Base Register specifies which set of debug registers is mapped into the debug register space (CAR0/1, DCR and DSR). In addition, a global debug status is available via the DBS. For more information, see Section 4.1.1 on page 4-1.

#### Compare Address Registers (CAR0/1)

The Compare Address Registers (CAR0 and CAR1) contain the address to be used to generate a breakpoint on an address or data. For more information, see Section 4.1.1 on page 4-1.

## **Debug Control Register (DCR)**

The Debug Control Register (DCR) holds the debug control bits. For more information, see Section 4.1.1 on page 4-1.

## **Debug Status Register (DSR)**

The Debug Status Register (DSR) holds the debug status bits. For more information, see Section 4.1.1 on page 4-1.

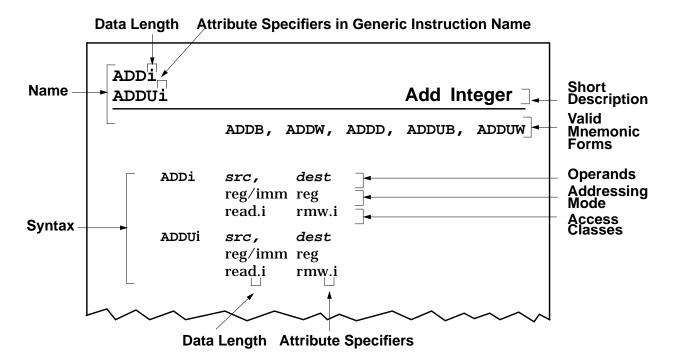

## 2.4 INSTRUCTION SET

The following table summarizes the CR16C instruction set. Chapter 5 and Appendix B describe each instruction in detail. Also refer to "Instructions Table Glossary" on page 2-11.

| Mnemonic   | Operands                     | Description                                                                           |

|------------|------------------------------|---------------------------------------------------------------------------------------|

| MOVES      |                              |                                                                                       |

| MOVi       | Rsrc/imm, Rdest              | Move                                                                                  |

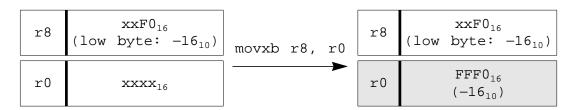

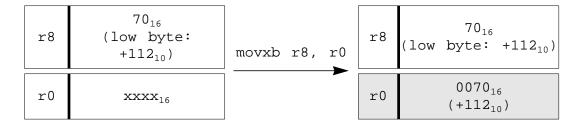

| MOVXB      | Rsrc, Rdest                  | Move with sign extension                                                              |

| MOVZB      | Rsrc, Rdest                  | Move with zero extension                                                              |

| MOVXW      | Rsrc, RPdest                 | Move with sign extension                                                              |

| MOVZW      | Rsrc, RPdest                 | Move with zero extension                                                              |

| MOVD       | imm, RPdest<br>RPsrc, RPdest | Move immediate to register-pair<br>Move between register-pairs                        |

| INTEGER AF | RITHMETIC                    |                                                                                       |

| ADD[U]i    | Rsrc/imm, Rdest              | Add                                                                                   |

| ADDCi      | Rsrc/imm, Rdest              | Add with carry                                                                        |

| ADDD       | RPsrc/Imm,RPdest             | Add with RP or immediate.                                                             |

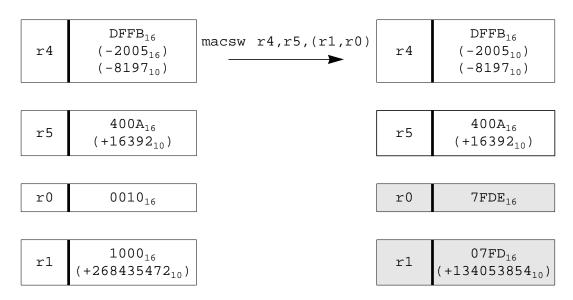

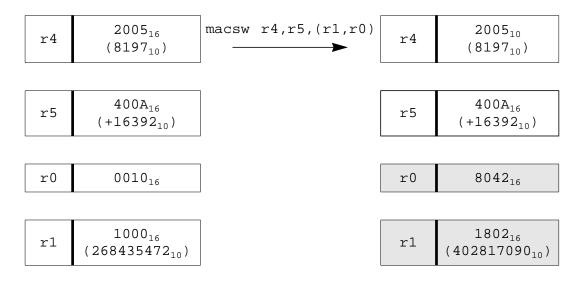

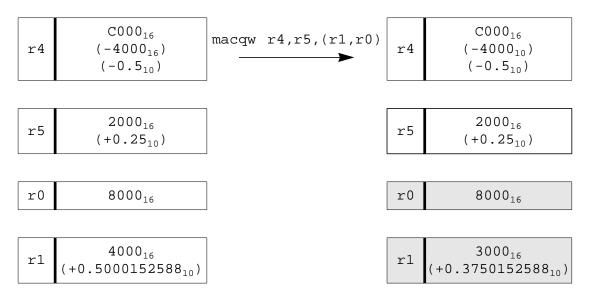

| MACQW      | Rsrc1 Rsrc2, RPdest          | Multiply signed Q15:<br>RPdest := RPdest + Rsrc1 * Rsrc2                              |

| MACSW      | Rsrc1 Rsrc2, RPdest          | Multiply signed and add result:<br>RPdest := RPdest + Rsrc1 * Rsrc2                   |

| MACUW      | Rsrc1 Rsrc2, RPdest          | Multiply unsigned and add result:<br>RPdest := RPdest + Rsrc1 * Rsrc2                 |

| MULi       | Rsrc/imm, Rdest              | Multiply: Rdest(8) := Rdest(8) * Rsrc(8)/Imm<br>Rdest(16) := Rdest(16) * Rsrc(16)/Imm |

| MULSB      | Rsrc, Rdest                  | Multiply: Rdest(16) := Rdest(8) * Rsrc(8)                                             |

| MULSW      | Rsrc, RPdest                 | Multiply: RPdest := RPdest(16) * Rsrc(16)                                             |

| MULUW      | Rsrc, RPdest                 | Multiply: RPdest := RPdest(16) * Rsrc(16);                                            |

| SUBi       | Rsrc/imm, Rdest              | Subtract: (Rdest := Rdest - Rsrc)                                                     |

| SUBD       | RPsrc/imm, RPdest            | Subtract: (RPdest := RPdest - RPsrc/imm)                                              |

| SUBCi      | Rsrc/imm, Rdest              | Subtract with carry: (Rdest := Rdest - Rsrc)                                          |

#### Mnemonic Operands

#### Description

INTEGER COMPARISON

| CMPi  | Rsrc/imm, Rdest   | Compare Rdest – Rsrc                      |  |  |  |  |  |  |

|-------|-------------------|-------------------------------------------|--|--|--|--|--|--|

| CMPD  | RPsrc/imm, RPdest | Compare RPdest-RPsrc                      |  |  |  |  |  |  |

| BEQ0i | Rsrc, disp        | Compare Rsrc to 0 and branch if EQUAL     |  |  |  |  |  |  |

| BNE0i | Rsrc, disp        | Compare Rsrc to 0 and branch if NOT-EQUAL |  |  |  |  |  |  |

#### LOGICAL AND BOOLEAN

| ANDi  | Rsrc/imm, Rdest   | Logical AND: Rdest := Rdest & Rsrc/Imm            |

|-------|-------------------|---------------------------------------------------|

| ANDD  | RPsrc/imm, RPdest | Logical AND: RPdest := RPsrc & RPsrc/Imm          |

| ORi   | Rsrc/imm, Rdest   | Logical OR: Rdest := Rdest   Rsrc/Imm             |

| ORD   | RPsrc/imm, RPdest | Logical OR: Rdest := RPdest   RPsrc/Imm           |

| Scond | Rdest             | Save condition code as boolean                    |

| XORi  | Rsrc/imm, Rdest   | Logical exclusive OR: Rdest := Rdest ^ Rsrc/Imm   |

| XORD  | RPsrc/imm, RPdest | Logical exclusive OR: Rdest := RPdest ^ RPsrc/Imm |

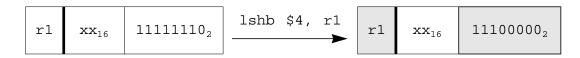

#### SHIFTS

| ASHUi | Rsrc/imm, Rdest  | Arithmetic left/right shift |  |

|-------|------------------|-----------------------------|--|

| ASHUD | Rsrc/imm, RPdest | Arithmetic left/right shift |  |

| LSHi  | Rsrc/imm, Rdest  | Logical left/right shift    |  |

| LSHD  | Rsrc/imm, RPdest | Logical left/right shift    |  |

#### **BIT OPERATIONS**

| SBITi | Iposition, disp(Rbase)<br>Iposition, disp(RPbase)<br>Iposition, (Rindex)disp(RPbasex)<br>Iposition, abs<br>Iposition, (Rindex)abs | Set a bit in memory      |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| CBITi | Iposition, disp(Rbase)<br>Iposition, disp(RPbase)<br>Iposition, (Rindex)disp(RPbasex)<br>Iposition, abs<br>Iposition, (Rindex)abs | Clear a bit in memory    |

| TBIT  | Rposition/imm, Rsrc                                                                                                               | Test a bit in a register |

| TBITi | Iposition, disp(Rbase)<br>Iposition, disp(RPbase)<br>Iposition, (Rindex)disp(RPbasex)<br>Iposition, abs<br>Iposition, (Rindex)abs | Test a bit in memory     |

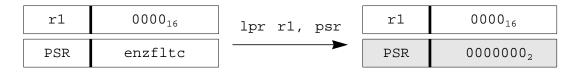

#### PROCESSOR REGISTER MANIPULATION

| LPR  | Rsrc, Rproc    | Load processor register         |

|------|----------------|---------------------------------|

| LPRD | RPsrc, Rprocd  | Load double processor register  |

| SPR  | Rproc, Rdest   | Store processor register        |

| SPRD | Rprocd, RPdest | Store double processor register |

#### Description

JUMPS AND LINKAGE

| Bcond  | disp9           | Conditional branch                                   |

|--------|-----------------|------------------------------------------------------|

|        | disp17          |                                                      |

|        | disp25          |                                                      |

| BAL    | RPlink, disp25  | Branch and link                                      |

| BR     | disp9           | Branch                                               |

|        | disp17          |                                                      |

|        | disp25          |                                                      |

| EXCP   | vector          | Trap (vector)                                        |

| Jcond  | RPtarget        | Conditional Jump to a large address                  |

| JAL    | RA, RPtarget,   | Jump and link to a large address                     |

|        | RPlink,RPtarget |                                                      |

| JUMP   | RPtarget        | Jump                                                 |

| JUSR   | RPtarget        | Jump and set PSR.U                                   |

| RETX   |                 | Return from exception                                |

| PUSH   | imm,Rsrc, RA    | Push "imm" number of registers on user stack, start- |

|        |                 | ing with Rsrc and possibly including RA              |

| POP    | imm, Rdest, RA  | Restore "imm" number of registers from user stack,   |

|        |                 | starting with Rdest and possibly including RA        |

| POPRET | imm, Rdest, RA  | Restore registers (similar to POP) and JUMP RA       |

#### LOAD AND STORE

| LOAD AND S |                                                                                                          |                                                                        |

|------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| LOADi      | disp(Rbase), Rdest                                                                                       | Load (register relative)                                               |

|            | abs,Rdest                                                                                                | Load (absolute)                                                        |

|            | (Rindex)abs, Rdest                                                                                       | Load (absolute index relative)                                         |

|            | (Rindex)disp(RPbasex), Rdest                                                                             | Load (register relative index)                                         |

|            | disp(RPbase), Rdest                                                                                      | Load (register pair relative)                                          |

| LOADD      | disp(Rbase), RPdest                                                                                      | Load (register relative)                                               |

|            | abs, RPdest                                                                                              | Load (absolute)                                                        |

|            | (Rindex)abs, RPdest                                                                                      | Load (absolute index relative)                                         |

|            | (Rindex)disp(RPbasex), RPdest                                                                            | Load (register pair index relative)                                    |

|            | disp(RPbase), RPdest                                                                                     | Load (register pair relative)                                          |

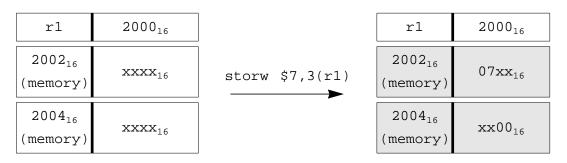

| STORi      | Rsrc, disp(Rbase)                                                                                        | Store (register relative)                                              |

|            | Rsrc, disp(RPbase)                                                                                       | Store (register pair relative)                                         |

|            | Rsrc, abs                                                                                                | Store (absolute)                                                       |

|            | Rsrc, (Rindex)disp(RPbasex)                                                                              | Store (register pair relative index)                                   |

|            | Rsrc, (Rindex)abs                                                                                        | Store (absolute index)                                                 |

| STORD      | RPsrc, disp(Rbase)                                                                                       | Store (register relative)                                              |

|            | RPsrc, disp(RPbase)                                                                                      | Store (register pair relative)                                         |

|            | RPsrc, abs                                                                                               | Store (absolute)                                                       |

|            | RPsrc, (Rindex)disp(RPbasex)                                                                             | Store (register pair index relative)                                   |

|            | RPsrc, (Rindex)abs                                                                                       | Store (absolute index relative)                                        |

| STOR IMM   | imm4, disp(Rbase)<br>imm4, disp(RPbase)<br>imm4, (Rindex)disp(RPbasex)<br>imm4, abs<br>imm4, (Rindex)abs | Store 4 bit immediate value in memory                                  |

| LOADM      | imm3                                                                                                     | Load 1 to 8 registers (R2-R5, R8-R11) from memory starting at (R0)     |

| LOADMP     | imm3                                                                                                     | Load 1 to 8 registers (R2-R5, R8-R11) from memory starting at (R1, R0) |

| STORM      | imm3                                                                                                     | Store 1 to 8 registers (R2-R5, R8-R11) to memory starting a (R1)       |

| STORMP     | imm3                                                                                                     | Store 1 to 8 registers (R2-R5, R8-R11) to memory starting a (R7, R6)   |

|            | -                                                                                                        | 1                                                                      |

#### Mnemonic Operands

#### Description

|                                                                   | •                                                                                                                                                                                 | -                                                                                                               |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| MISCELLANE                                                        | OUS                                                                                                                                                                               |                                                                                                                 |

| CINV                                                              | [d, i, u]                                                                                                                                                                         | Cache Invalidate                                                                                                |

| DI                                                                |                                                                                                                                                                                   | Disable maskable interrupts                                                                                     |

| EI                                                                |                                                                                                                                                                                   | Enable maskable interrupts                                                                                      |

| EIWAIT                                                            |                                                                                                                                                                                   | Enable maskable interrupts and wait for interrupt                                                               |

| NOP                                                               |                                                                                                                                                                                   | No operation                                                                                                    |

| WAIT                                                              |                                                                                                                                                                                   | Wait for interrupt                                                                                              |

| Instructions                                                      | Table Glossary                                                                                                                                                                    |                                                                                                                 |

| Rsrc - Sour<br>Rdest - Desti<br>Rbase - Base                      | ce register R???<br>nation register R???<br>register for relative addressing F                                                                                                    |                                                                                                                 |

| Rprocd- Proc<br>Rlink - Link<br>Rtarget- Targ                     | essor registers (CAR0/1, DCRL/H<br>essor registers Double (CAR0/1,<br>register R??? holding the address<br>et register R???. The register hol<br>or R13 used as an index register | DCR. DSR, PSR, ISP, etc.)<br>s of the next sequential address (return address).<br>lds a code address           |

| Rposition- Bi                                                     | t position register R??? - only the                                                                                                                                               | e lower 4-bits are used as bit position in TBIT                                                                 |

| RP???- Any (                                                      | when SR= 1: ((R1,R0) (R2,I                                                                                                                                                        | R1)(R11,R10), (R12_L,R11), R12, R13,RA,SP.)<br>R1)(R11,R10), (R12_L,R11),<br>_L),(RA_L, R13_L),(SP_L,RA_L),SP.) |

| RPsrc - Sour                                                      | ce register pair RP???                                                                                                                                                            |                                                                                                                 |

|                                                                   | ination register pair RP???                                                                                                                                                       |                                                                                                                 |

|                                                                   | e register pair for relative address                                                                                                                                              |                                                                                                                 |

| <b>RPbasex</b> - Base register pair for relative addressing only: |                                                                                                                                                                                   |                                                                                                                 |

RPbasex- Base register pair for relative addressing only: (R1,R0), (R3,R2), (R5,R4), (R7,R6), (R9,R8), (R11,R10), (R4,R3), (R6,R5)

RPlink - Link register pair RP???. The link register holds the address of the next sequential address (return address).

RPtarget- Target register pair RP???. The register holds a code address.

RA - Return Address Register- used in push and pops to determine if the return address (RA) should be pushed/popped on/from stack.

i - in this table B = byte; W = word

imm - Immediate value 8 bits for byte, 16 bits for word, 32 bits for double

immn - Immediate value of n bits:

Iposition- Bit number of data stored in memory

(8) - 8-bits e.g. the least significant byte of any R???

(16) - 16-bits e.g. a complete word register (R0..R11) or the least significant word of a double register (R12\_L,R13\_L,RA\_L,SP\_L)

abs - Absolute address - always unsigned

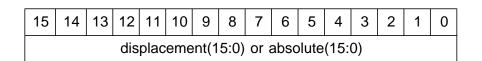

dispn - displacement of n bits - unsigned<sup>a</sup> for loads, stores and bitops, signed for branches

a. For CR16B compatibility LOAD/STOR (Rbase/RPbase) allow a negative displacement as well.

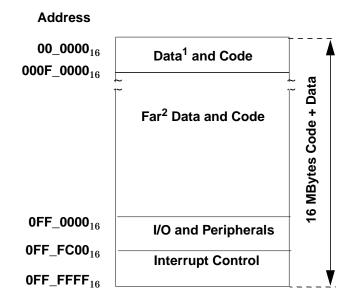

## 2.5 MEMORY ORGANIZATION

The CR16C provides access to 16M of memory. The memory is a uniform linear address space numbered sequentially starting at 0. CR16C data addressing is always byte-related (i.e., data can be addressed at byteresolution). The instructions, by contrast, are always word-aligned, and therefore instruction addresses are always even.

Memory can be logically divided into the following regions (see Figure 2-4):

- 0 1M-64K (0 through  $0E_FFFF_{16}$ ) This region can be accessed efficiently for data-manipulation using all addressing modes. Therefore, it should be used for RAMs. There are no restrictions on code in this region.

- 1M-64K 16M-64K (0F\_0000<sub>16</sub> through 0FE\_FFFF<sub>16</sub>)

This region can be accessed for data-manipulation using all addressing modes. However there are some limitations and disadvantages when accessing data in this region (accessing data in absolute mode requires a longer instruction, a label in this region cannot be used as a displacement and moving or adding a data label to a register pair requires a longer instruction). There are no restrictions on code in this region. Therefore, use this address range for code and infrequently used data.

- 16M-64K 16M-1K ( $0FF_{0000_{16}}$  through  $0FF_{FBFF_{16}}$ ) This region is reserved for I/O devices and peripherals. Loads, stores and bit operations using absolute addressing mode in this range are as efficient as in the range 0 - 1M-64K. This is because the core maps absolute addresses  $0F_{0000}$  through  $0F_{FFFF}$  to  $0FF_{0000}$ through  $0FF_{FFFF}$ .

- 16M-1K 16M-1 (0FF\_FC00<sub>16</sub> through 0FF\_FFFF<sub>16</sub>) This region is reserved for the Interrupt Controller Unit and its acknowledge address, as well as other internal uses.

For more information on the addressing modes see Sections 2.6 and 6.2 as well as Appendix B.

1 Efficient data access

2 Less efficient data access (Notation used in National CompactRISC Toolset. For notation used in other toolsets, see the appropriate documentation)

Figure 2-4. Memory Organization

#### 2.5.1 Data References

Data memory is byte-addressable in the CompactRISC architecture and organized in little-endian format, where the LSB within a word or a double-word resides at the lower address.

Figure 2-5. Bits are ordered from least significant to most significant. The least significant bit is in position zero. The TBIT, SBIT, and CBIT

instructions refer to bits by their ordinal position numbers. Figure 2-5 shows the memory representation for data values. **Data Representation**

DataThe CR16C supports references to memory by the LOAD and STORreferencesinstructions, as well as TBIT, SBIT, CBIT, PUSH, POP, LOADM and STORM.Bytes, words and double-words can be referenced on any boundary.

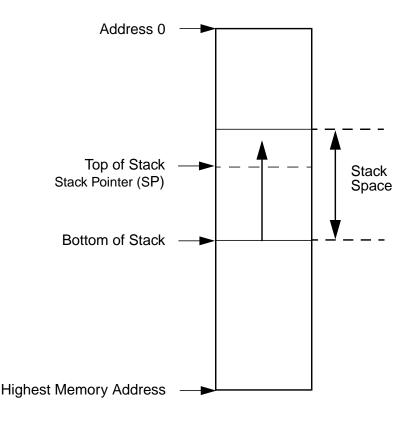

#### 2.5.2 Stacks

A stack is a one-dimensional data structure. Values are entered and removed, one item at a time, at one end of the stack, called the *top-of-stack*. The stack consists of a block of memory, and a variable called the *stack pointer*. The CR16C supports two types of stacks: the interrupt stack and the program stack.

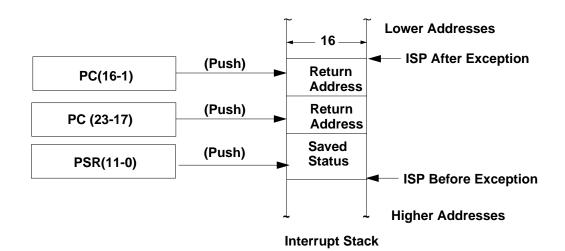

- **The interrupt stack** The processor uses the interrupt stack to save and restore the program state during the exception handling. This information is automatically pushed, by the hardware, onto the interrupt stack before entering an exception service procedure. On exit from the exception service procedure, the hardware pops this information from the interrupt stack. See Chapter 3 for more information. The interrupt stack pointer is accessed via the ISP Register.

- **The program stack** The program stack is normally used by programs at runtime, to save and restore register values upon procedure entry and exit. It is also used to store local and temporary variables. The program stack is accessed via the SP general-purpose register. Note that this stack is handled by software only, e.g., the CompactRISC C Compiler generates code that pushes data onto, and pops data from, the program stack. Only PUSH, POP and POPRET instructions adjust the SP automatically; otherwise, software must manage the SP during save and restore operations.

The user and supervisor stacks To support multi-tasking operating systems, support is provided for a two-level program stack: a user stack and a supervisor stack. The user stack pointer is accessed via the USP Register. The PSR contains a user mode status bit (PSR.U). When this user mode bit is set, the user stack pointer is used in place of SP for all operations. In addition, while in user mode, the PSR.U bit is read only. User mode is entered using the JUSR instruction, which causes a jump to the user program and entrance to user mode by setting the PSR.U bit. User mode is exited on any exception processing. While not in user mode, the user stack pointer can be accessed using the LPRD and SPRD instructions.

> Using the user stack can save memory required for the stack, since supervisor information can be saved instead on the supervisor stack each time a task is saved.

> An output signal is provided from the core (SFUSR) to indicate if the core is currently in user or supervisor mode. This may be used by a memory protection unit for checking accessed addresses in the various modes.

Both stacks expand toward address zero in memory.

## 2.6 ADDRESSING MODES

|                       | The CR16C supports these addressing modes: register/pair, immediate, relative, absolute, and indexaddressing. Memory is accessed by the generic load and store instructions, along with bit operations. These operations are supported with one or more of these modes.                                                  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | When register pairs are used, the lower bits are in the lower index register and the upper bits are in the higher index register. When CFG.SR=0, the double-word registers R12, R13, RA and SP are also considered register pairs. For more details, see Section 2.3.1.                                                  |

|                       | All references to register pairs should use parentheses. With a register pair, the lower numbered register pair should be on the right. For example,<br>jump (r5, r4)<br>load $$4(r4,r3)$ , (r6,r5)<br>load $$5(r12)$ , (r13)                                                                                            |

| Register/pair<br>mode | In register/pair mode, the operand is located in a general-purpose register, or in a general-purpose register pair (see Section 2.3.1). For example, the following instruction adds the contents of the low order byte of register r1 to the contents of the low order byte of r2, and places the result in register r2. |

|                       | ADDB r1, r2                                                                                                                                                                                                                                                                                                              |

| Immediate<br>mode     | In immediate mode, the operand is a constant value which is specified within the instruction. For example, the following instruction multiplies the value of r4 by 4 and places the result in r4:                                                                                                                        |

|                       | MULW \$4, r4                                                                                                                                                                                                                                                                                                             |

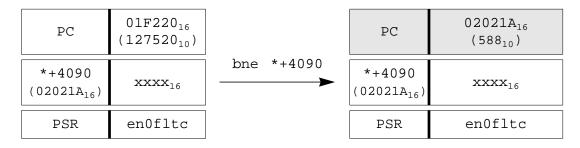

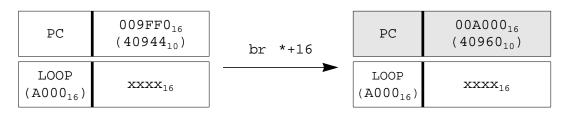

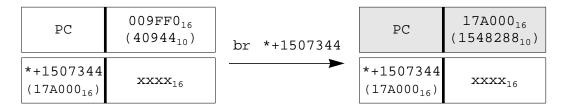

| Relative<br>mode      | In relative mode, the operand is obtained using a relative displacement<br>value encoded in the instruction. This displacement is relative to the<br>current Program Counter (PC) or general-purpose register or register<br>pair.                                                                                       |

|                       | In branch instructions, the displacement is always relative to the current value of the PC Register. For example the following instruction causes an unconditional branch to an address 10 ahead of the current PC.                                                                                                      |

|                       | BR *+10                                                                                                                                                                                                                                                                                                                  |

|                       | In load, store and bit operations, the displacement value is relative to the contents of a general-purpose register or register pair. For example, the following instruction loads the data contained at an address 12 higher than the contents of r5 into r6.                                                           |

|                       | LOADW 12(r5), r6                                                                                                                                                                                                                                                                                                         |

The following example loads the contents of memory at the address of the register pair (r5, r4) plus 4 into the register pair (r7, r6). r7 receives the high word and r6 receives the low word.

LOADD 4(r5, r4), (r7, r6)

Absolute In absolute mode, the operand is located in memory, and its address is specified explicitly within the instruction (normally 20 or 24 bits). For example, the following instruction loads the byte at addresses 4000 into the lower 8 bits of register 6.

LOADB 4000, r6

**Index mode** In index mode, the operand is located in memory. This mode supports load, store and bit operations, and is provided in order to handle relocatable code. CFG.SR must be 0 to use this addressing mode. Register R12 or R13 is used to hold a base index address to which absolute or relative mode addresses are added. For example the following instruction loads the word at address (r12) + (r5,r4) + 4 into r6.

LOADW [r12]4(r5,r4), r6

- For relative mode instructions, the memory address is obtained using the value of either R12 or R13, and adding the value of a register pair and a displacement. The displacement can be a 14 or 20-bit unsigned value, which is encoded in the instruction.

- For absolute mode instructions, the memory address is obtained using the value of either R12 or R13, and adding a 20-bit absolute address label which is encoded in the instruction.

For a more detailed explanation, see Section B.2 on page B-2.

For data addressing, Table 2-1 summarizes the size of the instruction along with the displacement sizes supported. Note that index addressing mode is not available when CFG.SR is set.

| Instructions          | Data relative to   | Instruction Size   |                     |         |

|-----------------------|--------------------|--------------------|---------------------|---------|

| instructions          |                    | 1 Word             | 2 Words             | 3 Words |

| Load/Store<br>(b/w/d) | register pair      | disp4              | disp16              | disp20  |

|                       | register           | disp0 <sup>a</sup> | disp14 <sup>a</sup> | disp20  |

|                       | index <sup>b</sup> | disp0              | disp14, abs20       | disp20  |

|                       | abs                |                    | abs20               | abs24   |

Table 2-1. Instruction Sizes Supported

| Instructions                 | Data relative to   | Instruction Size |                     |         |

|------------------------------|--------------------|------------------|---------------------|---------|

|                              |                    | 1 Word           | 2 Words             | 3 Words |

| (c/s/t)bit(b/w)<br>Store Imm | register pair      | disp0            | disp16              | disp20  |

|                              | register           |                  | disp14 <sup>a</sup> | disp20  |

|                              | index <sup>b</sup> |                  | disp14, abs20       | disp20  |

|                              | abs                |                  | abs20               | abs24   |

a. when CFG.SR = 1

b. when CFG.SR = 0

The data addressing modes supported for all instructions are identical in two and three-word formats. The instructions encoded in one word give priority to addressing relative to a register pair. This page is intentionally blank.

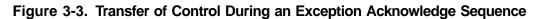

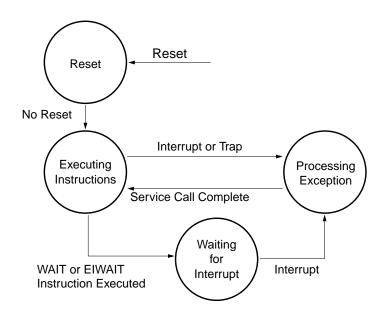

This chapter briefly describes exceptions and how they are handled, and provides detailed information on exception processing.

#### 3.1 INTRODUCTION

Program *exceptions* are conditions that alter the normal sequence of instruction execution, causing the processor to suspend the current process and execute a special service procedure, often called a *handler*.

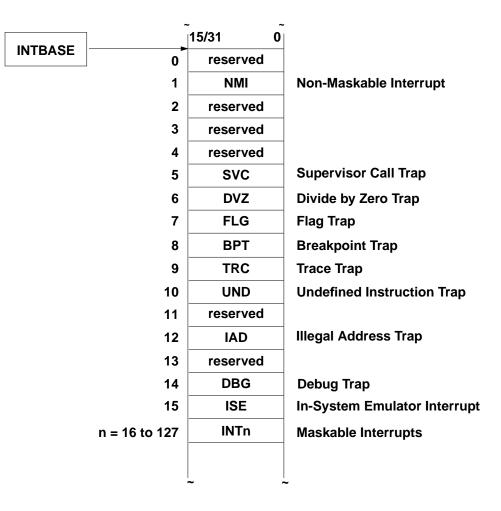

**Exception types and handling** An exception resulting from the activity of a source external to the processor is known as an *interrupt*; an exception which is initiated by some action or condition in the program itself is called a *trap*. Thus, an interrupt need have no relationship to the executing program, while a trap is caused by the executing program and recurs each time the program is executed. The CR16C recognizes twelve exceptions: nine traps and three types of interrupts.

> The exception-handling technique employed by an interrupt-driven processor determines how fast the processor can perform input/output transfers, the speed for transfers between tasks and processes, and the software overhead required for both these activities. Thus, to a large extent, it determines the efficiency of a processor's multi-programming and multi-tasking (including real-time) capabilities.

> Exception-handling in the CR16C uses a dispatch table. This table contains an entry for each exception, which holds the address of the exception handler. Once an exception is encountered, the processor uses the exception number to access the table and extract the handler address.

**Stack types** The CR16C features an interrupt stack, a supervisor stack and a user stack. The processor uses the interrupt stack solely for saving the PC and the PSR Register values during exception processing. This process occurs in hardware, without software intervention. The software uses the supervisor and user stacks to save register values and to pass parameters upon subroutine entry and subroutine calls. These stacks are managed by software using the PUSH, POP and POPRET instructions.

This stack architecture provides the following benefits:

- The essentials of the processor's state (PC and PSR) are saved correctly on the interrupt stack, even during nested, non-maskable interrupts. This process does not need to rely on disabling interrupts to allow software to save PC and PSR values on the interrupt stack.

- As the processor saves just the PC and PSR when exceptions occur, interrupt latency is kept at a minimum. During exception handling, the software need only save the registers it modifies, thus minimizing interrupt response time, and saving memory.

The<br/>exception<br/>processWhen an exception occurs, the CPU automatically preserves the state of<br/>the program immediately prior to the handling of the exception: a copy<br/>of the PC and the PSR is made and pushed onto the interrupt stack.<br/>The contents of the PSR is adjusted for exception processing. The inter-<br/>rupt exception number is then used to obtain the address of the excep-<br/>tion service procedure from the dispatch table, which is then called.

The **RETX** instruction returns control to the interrupted program, and restores the contents of the PSR and the PC registers to their previous status. See "RETX Return from Exception" on page 5-52.

#### 3.2 INTERRUPT HANDLING

The CR16C provides three types of interrupts: non-maskable (NMI), maskable, and In-System Emulator (ISE).

- Non-Maskable NMI are used for events which require immediate handling to preserve system integrity (such as an imminent power failure), and cannot be disabled. NMI use vector number 1 in the dispatch table. When an NMI is detected, the CR16C performs an interrupt-acknowledge bus cycle to address 0FF\_FF00<sub>16</sub>, and discards the byte that is read during that bus cycle.

- Maskable interrupts are disabled whenever PSR.E or PSR.I are 0. PSR.I serves as the global interrupt mask, while PSR.E serves as a local interrupt mask. PSR.E can be easily changed with the EI and DI instructions (see "EI Enable Maskable Interrupts" on page 5-20 and "DI Disable Maskable Interrupts" on page 5-19). PSR.E is used when interrupt-disabling is needed for a short period of time (e.g. when a read-modify-write sequence of instructions, accessing a semaphore, must not be interrupt-ed by another task).

On receipt of a maskable interrupt, the processor determines the vector number by performing an interrupt acknowledge bus cycle in which a byte is read from address  $OFF_FE00_{16}$ . This byte contains a number in the range 16-127 (the vector), which is used as an index in the dispatch table to find the address of the appropriate interrupt handler. Control is then transferred to that interrupt handler.

**In-System Emulator(ISE) interrupts ISE** interrupts cannot be disabled; they are reserved for system debug implementation. ISE interrupts use vector number 15 in the dispatch table. When an ISE interrupt is detected, the CR16C performs an interrupt-acknowledge bus cycle to address 0FF\_FC00<sub>16</sub>, and discards the byte that is read during that bus cycle.

#### 3.3 TRAPS

|                                   | The CR16C recognizes the following traps:                                                                                                                                                                                                                                                                                                         |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Breakpoint<br>(BPT)               | BPT is used for program debugging. Caused by the EXCP BPT instruction.                                                                                                                                                                                                                                                                            |

| Supervisor<br>Call (SVC)          | SVC temporarily transfers control to supervisor software, typically to access facilities provided by the operating system. It is caused by the EXCP SVC instruction.                                                                                                                                                                              |

| Flag (FLG)                        | FLG Indicates various computational exceptional conditions. it is caused<br>by the <b>EXCP FLG</b> instruction.                                                                                                                                                                                                                                   |

| Division by<br>Zero (DVZ)         | DVZ indicates an integer division by zero. It is caused by the EXCP DVZ instruction, which can be used by integer division emulation code to indicate this exception.                                                                                                                                                                             |

| Undefined<br>Instruction<br>(UND) | <ul> <li>UND indicates undefined opcodes. It is caused by an EXCP UND instruction, or an attempt to execute any of the following:</li> <li>any undefined instruction;</li> <li>the EXCP instruction when a reserved field is specified in the dispatch table (i.e., reserved trap number).</li> <li>an LPR/LPRD when PSR.U bit is set.</li> </ul> |

| lllegal<br>Address (IAD)          | IAD indicates that an illegal address was detected. For the CR16C, this trap is generated whenever an address outside the address range of 0 to 16M-1 is detected.                                                                                                                                                                                |

|                                   | Wraparound can happen either when the 16M boundary is crossed in a positive direction or when the 00_0000 address is crossed in a negative direction - and the resulting address yields in the illegal space. Both are trapped and flagged as illegal operations.                                                                                 |

|                                   | This is done primarily for reasons of future compatibility so that the ad-<br>dress range of the CR16C can easily be increased beyond 16M to main-<br>tain binary compatibility, without any issues of wraparound<br>compatibility.                                                                                                               |

The CR16C also provides an optional input for external illegal address detection, which can be used in the system to protect (unused) memory areas from being accessed by the core - this is not required in an AHB system like the CR16CPlus which provides an error response on the bus.

- **Trace (TRC)** TRC occurs before an instruction is executed when the PSR.P bit is 1. It is used for program debugging and tracing. See Chapter 4.

- **Debug (DBG)** A DBG trap occurs as a result of a breakpoint detected by the hardwarebreakpoint module, or by an external instruction-execute breakpoint using the tag mechanism through the BRKL line. It is used for instructionexecution and data-access breakpoints. See Chapter 4.

- **BPT, TRC and** DBG, TRC and BPT traps can also generate an interrupt acknowledge cycle for observability purposes, to alleviate the design of an ISE. This option can be selected by setting ADBG, ATRC, and ABPT bits respectively in the DCR Register. The addresses driven on the bus during these cycles are 0FF\_FC02<sub>16</sub> (DBG), 0FF\_FC0C<sub>16</sub> (TRC) and 0FF\_FC0E<sub>16</sub> (BPT) respectively. See Chapter 4.

#### 3.4 DETAILED EXCEPTION PROCESSING

#### **3.4.1 Instruction Endings**

The CR16C checks for exceptions at various points during the execution of instructions. Some exceptions, such as interrupts, are acknowledged between instructions, i.e., before the next instruction is executed. Other exceptions, such as a DVZ trap, are acknowledged during execution of an instruction. In such a case, the instruction is suspended. See Table 3-2.

If an instruction is suspended, it is not completed although all other previously issued instructions have been completed. Result operands and flags (except for the PSR.P bit on some traps) are not affected. When an instruction is suspended, the PC saved on the interrupt stack contains the address of the suspended instruction.

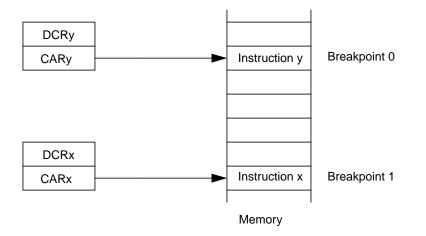

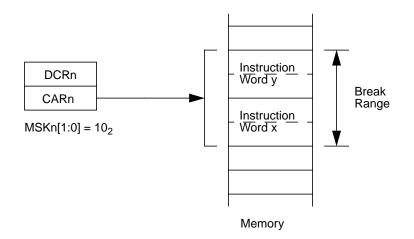

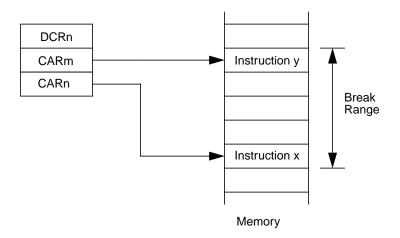

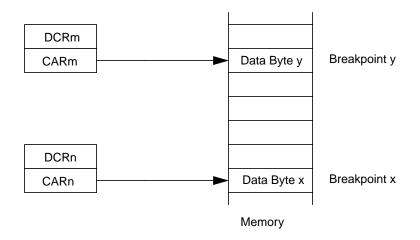

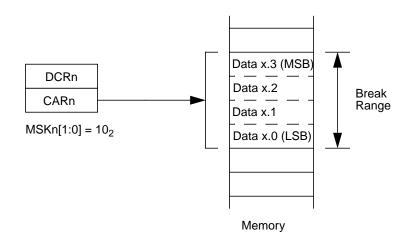

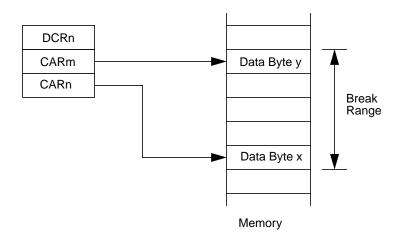

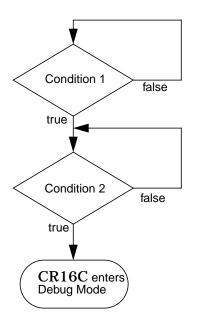

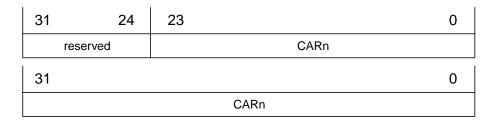

#### 3.4.2 The Dispatch Table