| MPW |

Tape-out |

Project Name |

Project Details |

Github |

Efabless |

Tapeout Link |

| MPW-2 |

18-June-2021 |

YiFive |

Single 32bit RISCV core without cache + SDRAM Controller + WB Interconnect |

Link |

Link |

Link |

| MPW-3 |

15-Nov-2021 |

Riscduino |

Single 32bit RISCV core without cache + Onchip SRAM + WB Interconnect |

Link |

Link |

Link |

| MPW-4 |

31-Dec-2021 |

Riscduino-R1 |

Single 32bit RISCV core with cache + Onchip SRAM + WB Inter Connect |

Link |

Link |

Link |

| MPW-5 |

21-Mar-2022 |

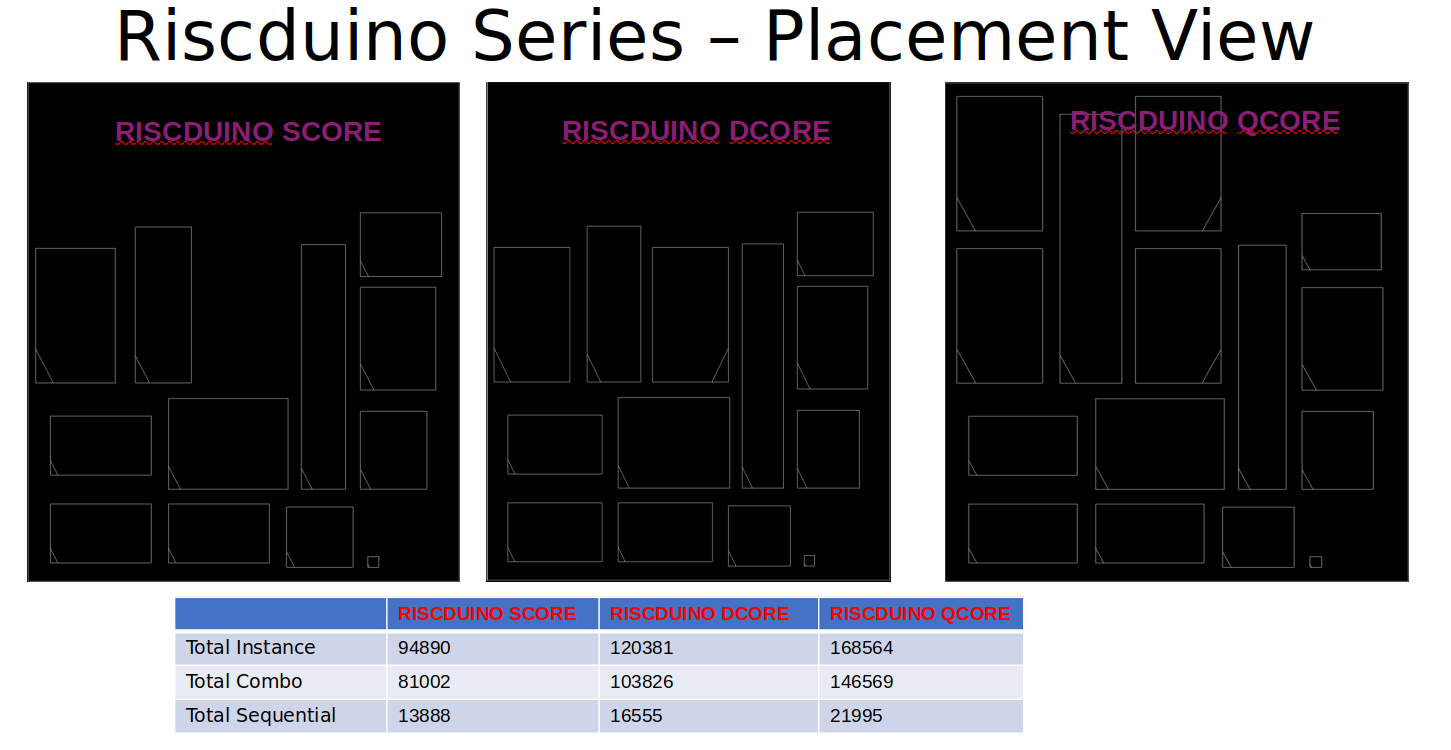

Riscduino-DCORE (D0) |

Dual 32bit RISCV core with cache + Onchip SRAM+ WB Cross Bar |

Link |

Link |

Link |

| MPW-5 |

21-Mar-2022 |

Riscduino-QCORE (Q0) |

Quad 32bit RISCV core with cache + Onchip SRAM+ WB Cross Bar |

Link |

Link |

Link |

| MPW-6 |

07-June-2022 |

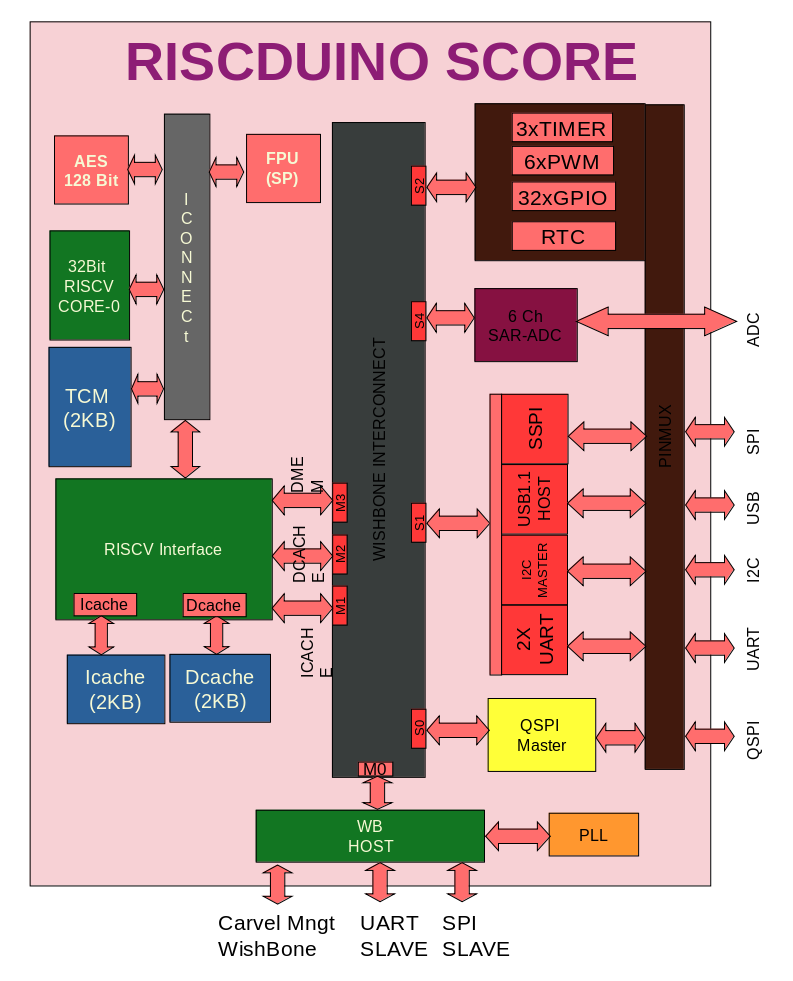

Riscduino-SCORE (S3) |

Single 32bit RISCV core with cache + Onchip SRAM+ WB Cross Bar |

Link |

Link |

Link |

| MPW-6 |

07-June-2022 |

Riscduino-DCORE (D1) |

Dual 32bit RISCV core with cache + Onchip SRAM+ WB Cross Bar |

Link |

Link |

Link |

| MPW-6 |

07-June-2022 |

Riscduino-QCORE (Q1) |

Quad 32bit RISCV core with cache + Onchip SRAM+ WB Cross Bar |

Link |

Link |

Link |

| MPW-7 |

12-Sept-2022 |

Riscduino-SCORE (S4) |

Single 32bit RISCV core with cache + Onchip SRAM+ WB Cross Bar |

Link |

Link |

Link |

| MPW-7 |

12-Sept-2022 |

Riscduino-DCORE (D3) |

Dual 32bit RISCV core with cache + Onchip SRAM+ WB Cross Bar |

Link |

Link |

Link |

| MPW-7 |

12-Sept-2022 |

Riscduino-QCORE (Q1) |

Quad 32bit RISCV core with cache + Onchip SRAM+ WB Cross Bar |

Link |

Link |

Link |

| MPW-8 |

31-Dec-2022 |

Riscduino-DCORE (D4) |

Dual 32bit RISCV core with cache + Onchip SRAM+ WB Cross Bar |

Link |

Link |

Link |

| MPW-8 |

12-Sept-2022 |

Riscduino-QCORE (Q3) |

Quad 32bit RISCV core with cache + Onchip SRAM+ WB Cross Bar |

Link |

Link |

Link |

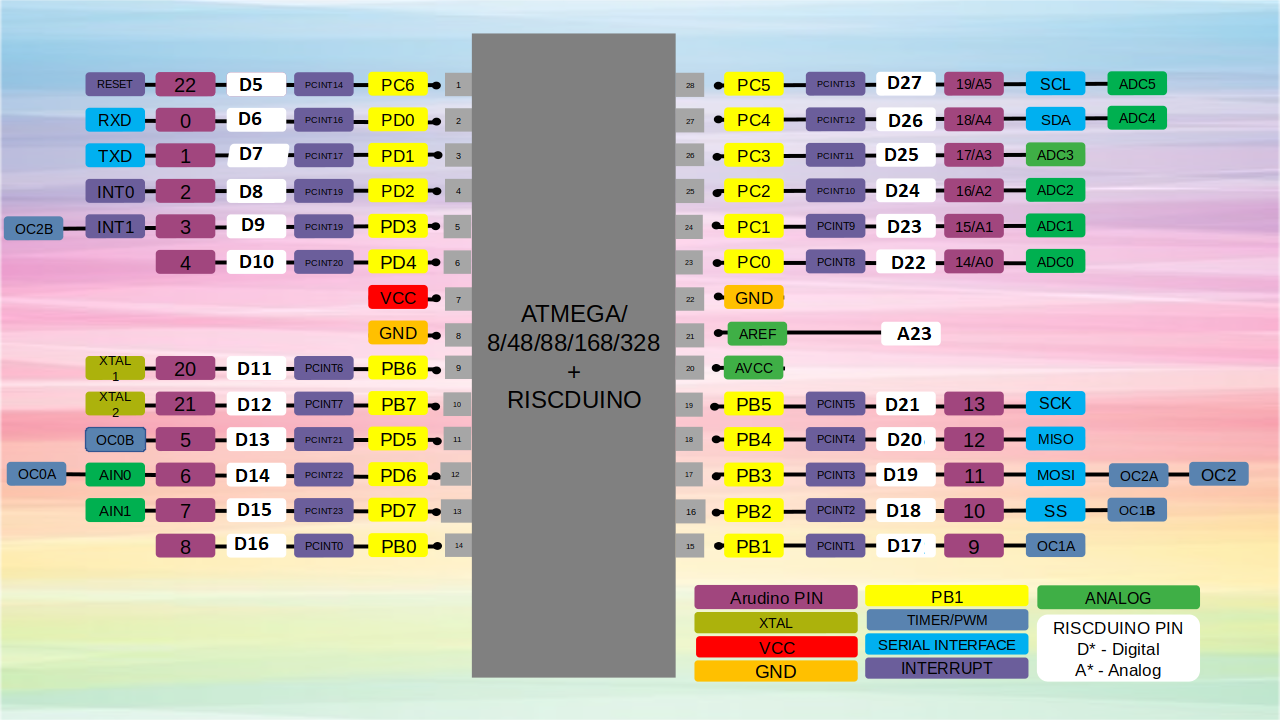

# SOC Pin Mapping

Carvel SOC provides 38 GPIO pins for user functionality. Riscduino SOC GPIO Pin Mapping as follows vs ATMEGA328 and Arudino

| ATMGA328 Pin No | Functionality | Arudino Pin Name | Carvel Pin Mapping |

| Pin-1 | PC6/RESET | D20 | digital_io[5] |

| Pin-2 | PD0/RXD[0] | D0 | digital_io[6] |

| Pin-3 | PD1/TXD[0] | D1 | digital_io[7]/analog_io[0] |

| Pin-4 | PD2/RXD[1]/INT0 | D2 | digital_io[8]/analog_io[1] |

| Pin-5 | PD3/INT1/OC2B(PWM0) | D3 | digital_io[9]/analog_io[2] |

| Pin-6 | PD4/TXD[1] | D4 | digital_io[10]/analog_io[3] |

| Pin-7 | VCC | | - |

| Pin-8 | GND | | - |

| Pin-9 | PB6/XTAL1/TOSC1 | D21 | digital_io[11]/analog_io[4] |

| Pin-10 | PB7/XTAL2/TOSC2 | D22 | digital_io[12]/analog_io[5] |

| Pin-11 | PD5/SS[3]/OC0B(PWM1)/T1 | D5 | digital_io[13]/analog_io[6] |

| Pin-12 | PD6/SS[2]/OC0A(PWM2)/AIN0 | D6 | digital_io[14]/analog_io[7] |

| Pin-13 | PD7/A1N1 | D7 | digital_io[15]/analog_io[8] |

| Pin-14 | PB0/CLKO/ICP1 | D8 | digital_io[16]/analog_io[9] |

| Pin-15 | PB1/SS[1]OC1A(PWM3) | D9 | digital_io[17]/analog_io[10] |

| Pin-16 | PB2/SS[0]/OC1B(PWM4) | D10 | digital_io[18]/analog_io[11] |

| Pin-17 | PB3/MOSI/OC2A(PWM5) | D11 | digital_io[19]/analog_io[12] |

| Pin-18 | PB4/MISO | D12 | digital_io[20]/analog_io[13] |

| Pin-19 | PB5/SCK | D13 | digital_io[21]/analog_io[14] |

| Pin-20 | AVCC | | - |

| Pin-21 | AREF | | analog_io[23] |

| Pin-22 | GND | | - |

| Pin-23 | PC0/uartm_rxd/ADC0 | D14/A0 | digital_io[22]/analog_io[15] |

| Pin-24 | PC1/uartm/ADC1 | D15/A1 | digital_io[23]/analog_io[16] |

| Pin-25 | PC2/usb_dp/ADC2 | D16/A2 | digital_io[24]/analog_io[17] |

| Pin-26 | PC3/usb_dn/ADC3 | D17/A3 | digital_io[25]/analog_io[18] |

| Pin-27 | PC4/ADC4/SDA | D18/A4 | digital_io[26]/analog_io[19] |

| Pin-28 | PC5/ADC5/SCL | D19/A5 | digital_io[27]/analog_io[20] |

| Additional Pad used for Externam ROM/RAM/USB |

| Sflash | sflash_sck | | digital_io[28]/Analog[21] |

| SFlash | sflash_ss0 | | digital_io[29]/Analog[22] |

| SFlash | sflash_ss1/AREF | | digital_io[30]/Analog[23] |

| SFlash | sflash_ss2 | | digital_io[31]/Analog[24] |

| SFlash | sflash_ss3 | | digital_io[32]/Analog[25] |

| SFlash | sflash_io0 | | digital_io[33]/Analog[26] |

| SFlash | sflash_io1 | | digital_io[34]/Analog[27] |

| SFlash | sflash_io2 | | digital_io[35]/Analog[28] |

| SFlash | sflash_io3 | | digital_io[36] |

| DEBUG | dbg_clk_mon | | digital_io[37] |

| SPARE | PA0 | | digital_io[0] |

| SPARE | PA1 | D23 | digital_io[1] |

| SPARE | PA2 | D24 | digital_io[2] |

| SPARE | PA3 | | digital_io[3] |

| SPARE | PA4 | D25 | digital_io[4] |

# Riscduino documentation

* Riscduino documentation available at :

| RISC IMEM |

RISC DMEM |

EXT MAP |

Target IP |

| 0x0000_0000 to 0x0FFF_FFFF |

0x0000_0000 to 0x0FFF_FFFF |

0x0000_0000 to 0x0FFF_FFFF |

QSPI FLASH MEMORY |

| 0x1000_0000 to 0x1000_00FF |

0x1000_0000 to 0x1000_00FF |

0x1000_0000 to 0x1000_00FF |

QSPI Config Reg |

| 0x1001_0000 to 0x1001_003F |

0x1001_0000 to 0x1001_003F |

0x1001_0000 to 0x1001_003F |

UART |

| 0x1001_0040 to 0x1001_007F |

0x1001_0040 to 0x1001_007F |

0x1001_0040 to 0x1001_007F |

I2C |

| 0x1001_0080 to 0x1001_00BF |

0x1001_0080 to 0x1001_00BF |

0x1001_0080 to 0x1001_00BF |

USB |

| 0x1001_00C0 to 0x1001_00FF |

0x1001_00C0 to 0x1001_00FF |

0x1001_00C0 to 0x1001_00FF |

SSPI |

| 0x1001_01C0 to 0x1001_013F |

0x1001_01C0 to 0x1001_013F |

0x1001_01C0 to 0x1001_013F |

SSPI |

| 0x1002_0080 to 0x1002_00FF |

0x1002_0080 to 0x1002_00FF |

0x1002_0080 to 0x1002_00FF |

PINMUX |

| - |

- |

0x3080_0000 to 0x3080_00FF |

WB HOST |

# SOC Size

| Block | Total Cell | Combo | Seq |

| ------ | --------- | ----- | -------- |

| RISC | 47218 | 41230 | 5988 |

| QSPI | 9039 | 7526 | 1513 |

| UART_I2C_USB_SPI | 11793 | 8932 | 2861 |

| WB_HOST | 6508 | 5356 | 1152 |

| WB_INTC | 6949 | 5538 | 1411 |

| PINMUX | 11932 | 9327 | 2605 |

| PERIPHERAL | 5852 | 4791 | 1061 |

| FPU | 12831 | 11394 | 1437 |

| AES | 21549 | 17960 | 3589 |

| BUS-REPEATER | 922 | 922 | 0 |

| | | | |

| TOTAL | 134593 | 112976 | 21617 |

# Prerequisites

- Docker (ensure docker daemon is running) -- tested with version 19.03.12, but any recent version should suffice.

## Step-1: Docker in ubuntu 20.04 version

```bash

sudo apt update

sudo apt-get install apt-transport-https curl rtificates -agent software-properties-common

curl -fsSL https://download.docker.com/linux/ubuntu/gpg | sudo apt-key add -

sudo apt-get install apt-transport-https curl ca-certificates software-properties-common

sudo apt update

apt-cache policy docker-ce

sudo apt install docker-ce

#Add User Name to docker

sudo usermod -aG docker