# The gem5 Standard Library

A presentation by Bobby R. Bruce

### What is the standard library for?

When done without the library you must define *every* part of your simulation.

This allows for maximum flexibility but can mean creating 100s of lines of Python to create even a basic simulation.

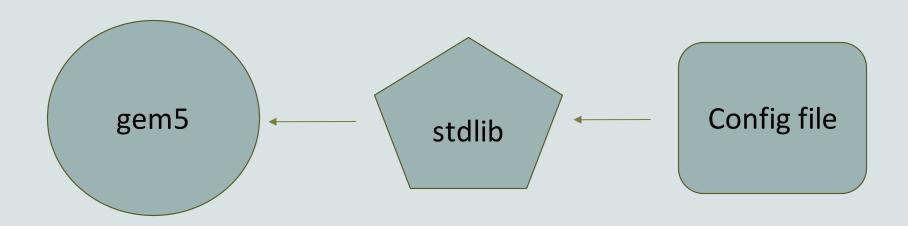

### What is the standard library for?

The stdlib is a library which allows for users to quickly create systems with pre-built components.

The stdlib's module architecture allows for components (e.g. a memory system or a cache hierarchy setup) to be quickly swapped in and out without radical redesign.

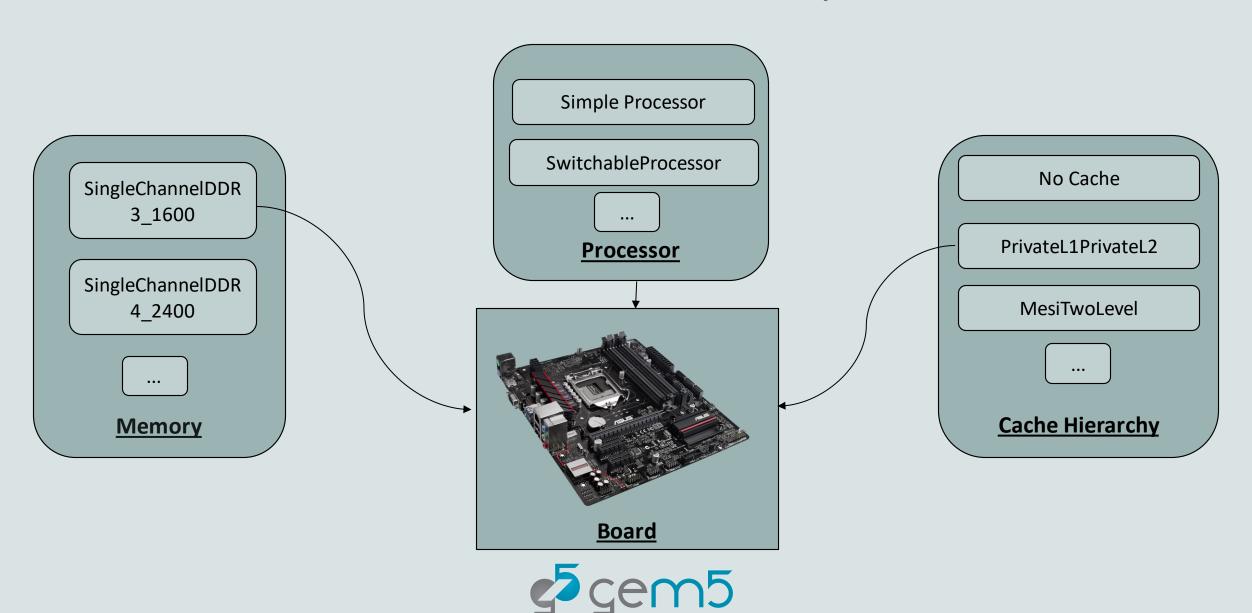

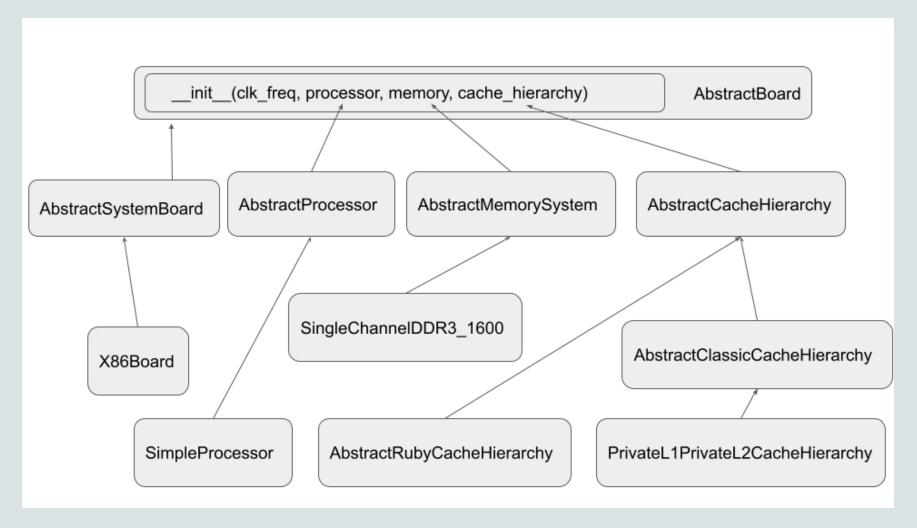

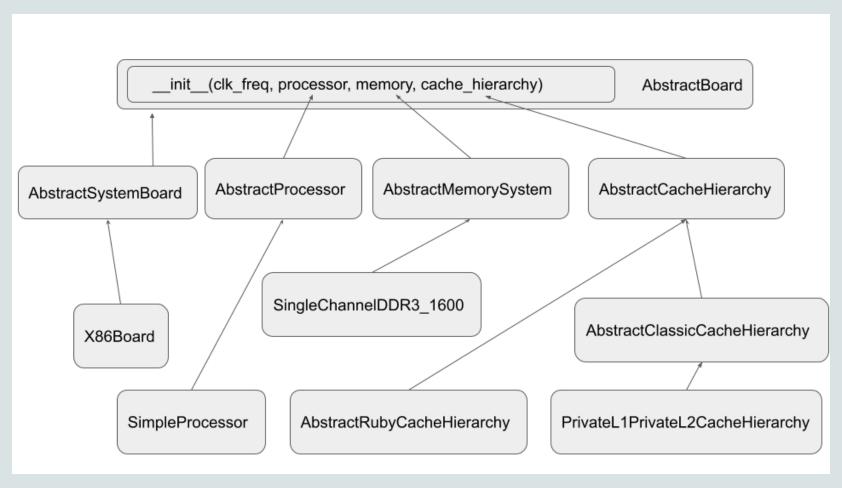

### The stdlib modular metaphor

### The modular architecture

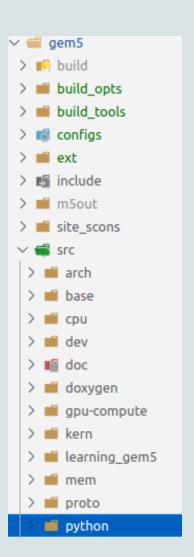

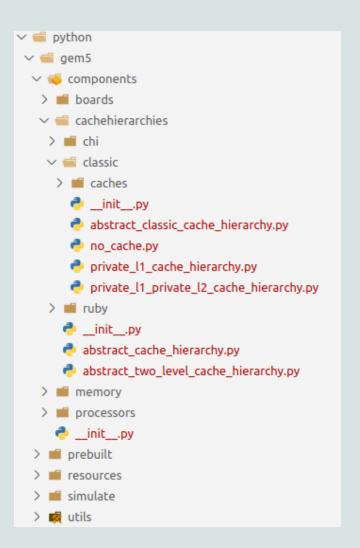

### Where to find stuff: The directory structure

### Where to find stuff: Importing in a script

```

> iii boards

> 📹 chi

> iii caches

init .pv

abstract classic cache hierarchy.py

no_cache.py

private_l1_cache_hierarchy.py

private_l1_private_l2_cache_hierarchy.py

> 📹 ruby

__init__.py

abstract_cache_hierarchy.py

abstract two level cache hierarchy.py

> memory

> iii processors

__init__.py

> ii prebuilt

> iii resources

simulate

> 🙀 utils

```

```

from gem5.components.boards.simple board import SimpleBoard

from gem5.components.cachehierarchies.classic.no cache import NoCache

from gem5.components.memory.single channel import SingleChannelDDR3_1600

from gem5.components.processors.simple processor import SimpleProcessor

from gem5.components.processors.cpu types import CPUTypes

from gem5.resources.resource import Resource

from gem5.simulate.simulator import Simulator

```

#### materials/using-gem5/02-stdlib/hello-world.py

```

from gem5.components.boards.simple board import SimpleBoard

from gem5.components.cachehierarchies.classic.no cache import NoCache

from gem5.components.memory.single channel import SingleChannelDDR3_1600

from gem5.components.processors.simple processor import SimpleProcessor

from gem5.components.processors.cpu types import CPUTypes

from gem5.resources.resource import Resource

from gem5.simulate.simulator import Simulator

```

```

# Obtain the components.

cache_hierarchy = NoCache()

memory = SingleChannelDDR3_1600("1GiB")

processor = SimpleProcessor(cpu_type=CPUTypes.TIMING, num_cores=1)

```

```

#Add them to the board.

board = SimpleBoard(

clk_freq="3GHz",

processor=processor,

memory=memory,

cache_hierarchy=cache_hierarchy,

)

```

### gem5 Resources

- gem5 resources is a repository providing resources that are known to be compatible with gem5.

- These resources are not necessary for the compilation or running gem5 but may aid users in running simulations. E.g.: disk images, kernels, applications, cross-compilers, etc.

- Resources are held on gem5's Google Cloud Bucket, and sources for these resources are found at: <a href="https://gem5.googlesource.com/public/gem5-resources/">https://gem5.googlesource.com/public/gem5-resources/</a>

- The stdlib can be used to automatically obtain and use these resources.

- https://resources.gem5.org/resources.json

### Looking up gem5 Resources

https://resources.gem5.org/resources.json

```

1 "resources": [

"resources": [

"type": "resource",

"name" : "riscv-disk-img",

"documentation" : "A simple RISCV disk image based on busybox.",

"architecture": "RISCV".

"is zipped" : true,

"md5sum" : "d6126db9f6bed7774518ae25aa35f153".

"url": "{url_base}/images/riscv/busybox/riscv-disk.img.gz",

10

"source": "src/riscv-fs",

11

12

"additional metadata" : {

"root partition": null

13

14

15

},

```

This is all machine-reachable for now. We're working on a web-portal.

### Obtaining Resources in the stdlib

materials/using-gem5/02-stdlib/obtaining-resources.py

```

from gem5.resources.resource import Resource

resource = Resource("riscv-disk-img")

print(f"The resources is available at {resource.get local path()}")

```

> gem5-x86 materials/using-gem5/02-stdlib/obtaining-resources.py

### Obtaining Resources in the stdlib

```

Resource 'riscv-disk-img' was not found locally. Downloading to '/home/bbruce/.cache/gem5/riscv-disk-img.gz'...

Finished downloading resource 'riscv-disk-img'.

Decompressing resource 'riscv-disk-img' ('/home/bbruce/.cache/gem5/riscv-disk-img.gz')...

Finished decompressing resource 'riscv-disk-img'.

The resources is available at /home/bbruce/.cache/gem5/riscv-disk-img

bbruce@liberty:~/Desktop/gem5-tutorial/gem5$ ./build/X86/gem5.opt ../materials/stdlib/obtaining-resources.py

gem5 Simulator System. http://gem5.org

gem5 is copyrighted software; use the --copyright option for details.

gem5 version 21.2.0.0

gem5 compiled May 16 2022 12:37:27

gem5 started May 16 2022 12:46:24

gem5 executing on liberty.cs.ucdavis.edu, pid 305928

command line: ./build/X86/gem5.opt ../materials/stdlib/obtaining-resources.py

The resources is available at /home/bbruce/.cache/gem5/riscv-disk-img

```

The stdlib will use the cached resources if already downloaded.

Run the script twice and see for yourself.

### Using a Custom Resource

You don't need to use the gem5 resources

You can specify a local resources (e.g., your own disk image)

```

from gem5.resources.resource import CustomResource

CustomResource("tests/test-progs/hello/bin/x86/linux/hello")

```

Back to "materials/using-gem5/02-stdlib/hello-world.py", add the following:

```

# Set the workload.

binary = Resource("x86-hello64-static")

board.set_se_binary_workload(binary)

```

`set\_se\_binary\_workload` is used to run a board in Syscall Emulation mode, with a single binary

#### Append the following:

```

# Setup the Simulator and run the simulation.

simulator = Simulator(board=board)

simulator.run()

```

```

from gem5.components.boards.simple_board import SimpleBoard

from gem5.components.cachehierarchies.classic.no_cache import NoCache

from gem5.components.memory.single_channel import SingleChannelDDR3_1600

from gem5.components.processors.simple_processor import SimpleProcessor

from gem5.components.processors.cpu_types import CPUTypes

from gem5.resources.resource import Resource

from gem5.simulate.simulator import Simulator

# Obtain the components.

cache hierarchy = NoCache()

memory = SingleChannelDDR3_1600("1GiB")

processor = SimpleProcessor(cpu_type=CPUTypes.TIMING, num_cores=1)

14

# Add them to the board.

board = SimpleBoard(

17

clk_freq="3GHz", processor=processor, memory=memory, cache_hierarchy=cache_hierarchy

18

19

# Set the workload.

binary = Resource("x86-hello64-static")

board.set_se_binary_workload(binary)

23

# Setup the Simulator and run the simulation.

simulator = Simulator(board=board)

simulator.run()

```

Save the file!!!

> gem5-x86 materials/using-gem5/02-stdlib/hello-world.py

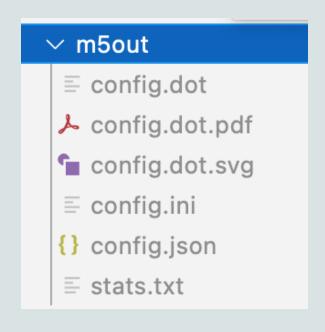

#### More detailed output

Look into the more the "gem5/m5out" directory

- The "config" files detail your system configuration (various formats, "config.ini" most human-readable.

- The stats.txt shows the various simulation statistics.

- In Full-System simulations the terminal output can be found in this directory.

### More detailed output

Look into the more the "gem5/m5out/stats.txt" file

| Begin Simulation | Statistics   |

|------------------|--------------|

| simSeconds       | 0.000005     |

| simTicks         | 4979349      |

| finalTick        | 4979349      |

| simFreq          | 100000000000 |

| hostSeconds      | 0.08         |

| hostTickRate     | 64410071     |

| hostMemory       | 1169600      |

| simInsts         | 6546         |

| simOps           | 12944        |

| hostInstRate     | 84513        |

| hostOpRate       | 167067       |

### Extending our design

Remember: gem5 is modular!

In general, you can replace components with components of the same type.

Let's add a real cache implementation to our design!

### Extending our design

```

#from gem5.components.cachehierarchies.classic.no_cache import NoCache

from gem5.components.cachehierarchies.classic.private l1 private l2 cache hierarchy import (

PrivateL1PrivateL2CacheHierarchy

)

```

```

# Obtain the components.

# cache_hierarchy = NoCache()

cache_hierarchy = PrivateL1PrivateL2CacheHierarchy(

lld_size="32KiB",

lli_size="32KiB",

lli_size="32KiB",

l2_size="64KiB"

)

memory = SingleChannelDDR3_1600("1GiB")

processor = SimpleProcessor(cpu_type=CPUTypes.ATOMIC, num_cores=1)

```

Save the file again.

> gem5-x86 materials/using-gem5/02-stdlib/hello-world.py

### Extending our design

Check the output in "m5out/stats.txt" and see how the Simulated Seconds and Simulated Ticks varies when using and not using a cache.

"materials/using-gem5/02-stdlib/x86-full-system.py"

```

from gem5.utils.requires import requires

from gem5.components.boards.x86 board import X86Board

from gem5.components.memory.single channel import SingleChannelDDR3_1600

from gem5.components.cachehierarchies.ruby.mesi two level cache hierarchy import MESITwoLevelCacheHierarchy

from gem5.components.processors.simple switchable processor import SimpleSwitchableProcessor

from gem5.coherence protocol import CoherenceProtocol

from gem5.isas import ISA

from gem5.resources.resource import Resource

from gem5.simulate.simulator import Simulator

from gem5.simulate.exit event import ExitEvent

```

```

requires(

isa_required=ISA.X86,

coherence_protocol_required=CoherenceProtocol.MESI_TWO_LEVEL,

)

```

This adds a check for the gem5 binary parsing the script. In this case:

- 1. The binary supports the X86 ISA.

- 2. The binary supports the MESI Two Level coherence protocol.

```

cache hierarchy = MESITwoLevelCacheHierarchy(

21

lld size="32KiB",

22

lld assoc=8,

23

lli size="32KiB",

24

lli assoc=8,

25

l2 size="256kB",

26

l2 assoc=16,

27

num l2 banks=1,

28

29

```

```

35 memory = SingleChannelDDR3_1600("2GiB")

```

```

processor = SimpleSwitchableProcessor(

starting_core_type=CPUTypes.TIMING,

switch_core_type=CPUTypes.03,

num_cores=2,

)

```

The SimpleSwitchingProcessor allows for different types of cores to be swapped during a simulation with `processor.switch()`.

This can be useful when wanting to switch to and from a detailed form of simulation.

As usual, we add the components to the board, in this case an `X86Board`.

```

command = "m5 exit;" \

63

+ "echo 'This is running on 03 CPU cores.';" \

64

+ "sleep 1;" \

65

+ "m5 exit:"

67

board.set kernel disk workload(

kernel=Resource("x86-linux-kernel-5.4.49",),

69

disk image=Resource("x86-ubuntu-18.04-img"),

70

readfile contents=command,

71

72

```

The 'set\_kernel\_disk\_workload` function is used to run a full system workload.

You must specify the `kernel` resource to use and the `disk\_image` resource.

In this case we can set the command to run on boot.

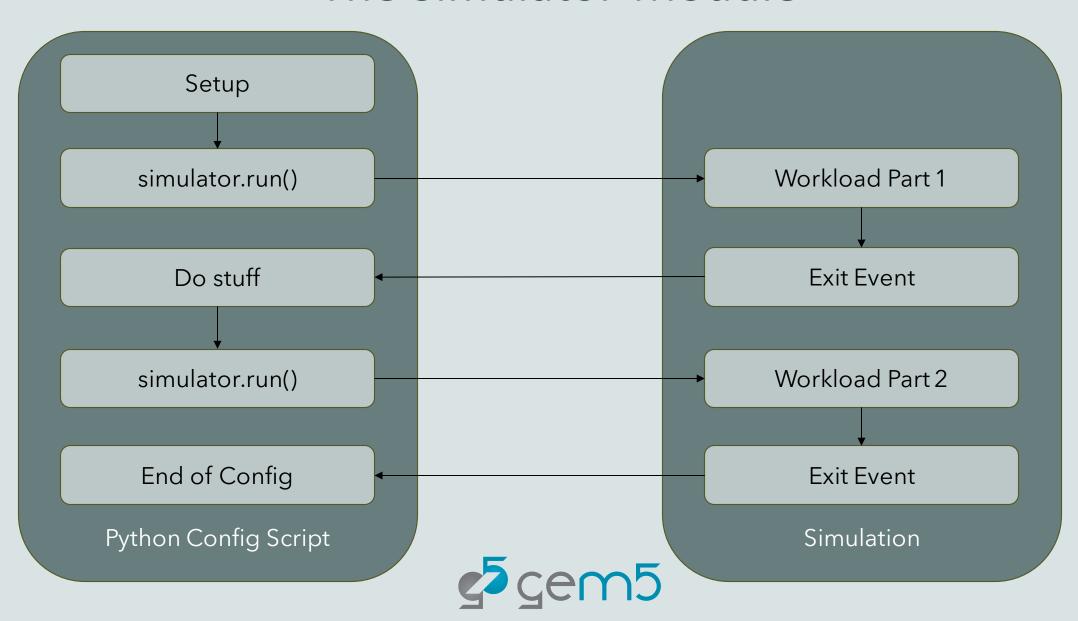

During a simulation you can have "Exit Events".

In this example there are two. These exit the simulation loop and return to the Python Script.

The Simulator Module is used to handle these events. Let's play with some examples to see how.

Go to "materials/using-gem5/02-stdlib/simulator-use.py"

```

# Obtain the components.

cache_hierarchy = NoCache()

10

11

memory = SingleChannelDDR3_1600("1GiB")

12

processor = SimpleProcessor(cpu_type=CPUTypes.ATOMIC, num_cores=1)

13

14

15

# Add them to the board.

16

board = SimpleBoard(

clk_freq="3GHz", processor=processor, memory=memory, cache_hierarchy=cache_hierarchy

17

18

19

20

# Set the workload.

binary = CustomResource(

21

"materials/using-gem5/02-stdlib/m5-exit-example/m5-exit-example"

22

23

board.set_se_binary_workload(binary)

24

25

# Setup the Simulator and run the simulation.

simulator = Simulator(board=board)

simulator.run()

```

This is a pretty normal looking script but we are running this "m5-exit-example" binary. Let's look into it

Go to "materials/using-gem5/02-stdlib/m5-exit-example/m5-exit-example.c"

```

#include <stdio.h>

#include "gem5/m5ops.h"

3

int main()

5

printf("The program has started!\n");

6

int exit count = 0;

8

while(1)

9

10

exit count++;

11

printf("About to exit the simulation for the %d st/nd/rd/st time\n", exit count);

12

m5 exit(0);

13

14

15

return 0;

16

17

```

Go back to "materials/using-gem5/02-stdlib/simulator-use.py"

```

# Setup the Simulator and run the simulation.

simulator = Simulator(board=board)

simulator.run()

print("We can do stuff after an m5 exit event. Prior to continuing the simulation")

simulator.run()

print("And again...")

simulator.run()

```

> gem5-x86 materials/using-gem5/02-stdlib/simulator-use.py

Let's be a bit cleverer...

```

# Setup the Simulator and run the simulation.

simulator = Simulator(

31

board=board,

32

on exit event={

33

ExitEvent.EXIT : (print(statement) for statement in ["Just exited the first exit event",

34

"Just exited the second call

"Just exited the third exit event"]),

35

36

37

38

simulator.run()

39

```

> gem5-x86 materials/using-gem5/02-stdlib/simulator-use.py

#### The Simulator Module

Here we're only covering the "Exit" type exit event, but there are other types.

You can override different types for different things.

The Simulator module has default behavior for each (see "gem5/src/python/gem5/simulate/exit\_event\_generators.py")

- ExitEvent.EXIT

- ExitEvent.CHECKPOINT

- ExitEvent.FAIL

- ExitEvent.SWITCHCPU

- ExitEvent.WORKBEGIN

- ExitEvent.WORKEND

- ExitEvent.USER\_INTERRUPT

- ExitEvent.MAX\_TICK

#### The Simulator Module

Note: This is module is still considered to be in Beta. The API may change in future versions of gem5

## An X86 full-system simulation

Let's go back to "materials/using-gem5/02-stdlib/x86-full-system.py"

```

simulator = Simulator(

board=board,

on_exit_event={

ExitEvent.EXIT : (func() for func in [processor.switch]),

},

}

simulator.run()

```

#### An X86 full-system simulation

We're done! You now have a full-system simulation!

> gem5-x86 materials/using-gem5/02-stdlib/x86-full-system.py

**Warning**: This will take a long time to complete execution.

Cntl+C to exit this.

Open "materials/using-gem5/02-stdlib/unique\_cache\_hierarchy/unique\_cache\_hierarchy/

```

from gem5.components.cachehierarchies.classic.abstract_classic_cache_hierarchy \

import AbstractClassicCacheHierarchy

from gem5.components.boards.abstract_board import AbstractBoard

3

from m5.objects import Port

6

class UniqueCacheHierarchy(AbstractClassicCacheHierarchy):

8

9

10 3

def __init__(self) -> None:

AbstractClassicCacheHierarchy.__init__(self=self)

11

12

def get_mem_side_port(self) -> Port:

13

14

pass

15

def get_cpu_side_port(self) -> Port:

16

17

pass

18

def incorporate_cache(self, board: AbstractBoard) -> None:

19

20

pass

```

Complete the constructor and declare the mem-side and cpu-side ports

```

def init (self) -> None:

17

AbstractClassicCacheHierarchy. init (self=self)

18

self.membus = SystemXBar(width=64)

19

20

def get_mem_side_port(self) -> Port:

21

return self.membus.mem side ports

22

23

def get cpu side port(self) -> Port:

24

return self.membus.cpu side ports

25

```

Next, open "materials/using-gem5/02-stdlib/unique\_cache\_hierarchy/l1cache.py"

```

from m5.objects import Cache, StridePrefetcher

class L1Cache(Cache):

pass

```

Let's extend the "Cache" SimObject to customize it for our purposes

```

class L1Cache(Cache):

A simple cache with default values.

def init (self):

super(). init ()

self.size = "32KiB"

11

12

self.assoc = 8

13

self.tag latency = 1

self.data latency = 1

14

self.response latency = 1

15

self.mshrs = 16

16

self.tgts per mshr = 20

17

self.writeback clean = True

18

self.prefetcher = StridePrefetcher()

19

```

#### **Important note:**

SimObject member variables are special. You can only set SimObject variables. Code like `self.custom\_variable = 7` will cause an error.

If you want create a non-SimObject variable, the variable name must have a preceding underscore:

`self.\_custom\_variable = 7`

#### Go back to

"materials/using-gem5/02-stdlib/unique\_cache\_hierarchy/unique\_cache\_hierarchy.py"

```

def incorporate cache(self, board: AbstractBoard) -> None:

27

28

# Set up the system port for functional access from the simulator.

board.connect system port(self.membus.cpu side ports)

29

30

for cntr in board.get memory().get memory controllers():

31

cntr.port = self.membus.mem side ports

32

You, 10 minutes ago • Update materials for adding unique cache hierar

33

34

self.llicaches = [

L1Cache()

35

for i in range(board.get processor().get num cores())

36

37

38

self.l1dcaches = [

39

L1Cache()

40

for i in range(board.get processor().get num cores())

41

42

```

```

for i, cpu in enumerate(board.get processor().get cores()):

44

45

cpu.connect icache(self.llicaches[i].cpu side)

46

cpu.connect dcache(self.lldcaches[i].cpu side)

47

48

self.l1icaches[i].mem side = self.membus.cpu side ports

49

self.lldcaches[i].mem side = self.membus.cpu side ports

50

51

int req port = self.membus.mem side ports

52

int resp port = self.membus.cpu side ports

53

cpu.connect interrupt(int req port, int resp port)

54

```

Try adding this cache hierarchy to your "hello-world.py" example.

It can be done via a standard Python import.

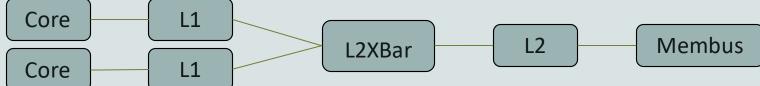

### Create your own cache!!

As a challenge, create your own gem5 Private L1 Shared L2 Cache hierarchy.

Once done, modify your "hello-world.py" program to see the performance difference of using the Private L1 with a Private L2 Cache hierarchy vs a Private L1 with a Shared L2 Cache.

Helpful: `from m5.objects import L2XBar`

"src/python/gem5/components/cachehierarchies/classic" contains the code for a Private L1 Cache Hierarchy and a PL1/PL2 Cache Hierarchy. It may be helpful to reference them.