AMERICAN MICRO-SYSTEMS, INC. S9021 DYNAMIC KEYBOARD ENCODER JANUARY 1973

### **FEATURES**

- 3600 Bit ROM programmed by altering one mask

- 90 Key encoding

- 4 Modes

- Shift control lockout

- 10 Data outputs plus a strobe (data ready signal)

- Zener protected inputs

- Shift lock I/O provides 300  $\mu$ a lamp drive

- TTL/DTL compatible shift, control, and keyboard

- Input Hysteresis

- TTL/DTL compatible data outputs without pull-up resistors or clamping diodes

- Less than 200 mW power dissipation

- Variable switch bounce masking up to 5 milliseconds

- Internal clock with external frequency control

- Three state outputs for bussing with other encoder circuits

- Latched outputs retain last valid code

### MASK PROGRAMMED OPTIONS

- Static\* or pulse output data strobe

- Input hysteresis\*

- MOS\* (15K $\Omega$ ) or TTL (5K $\Omega$ ) compatible resistor to V<sub>SS</sub> on inputs from keyboard)

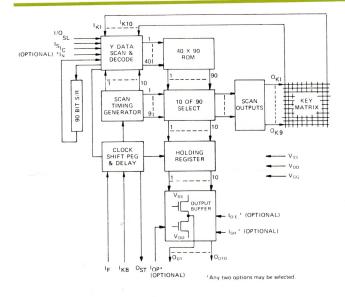

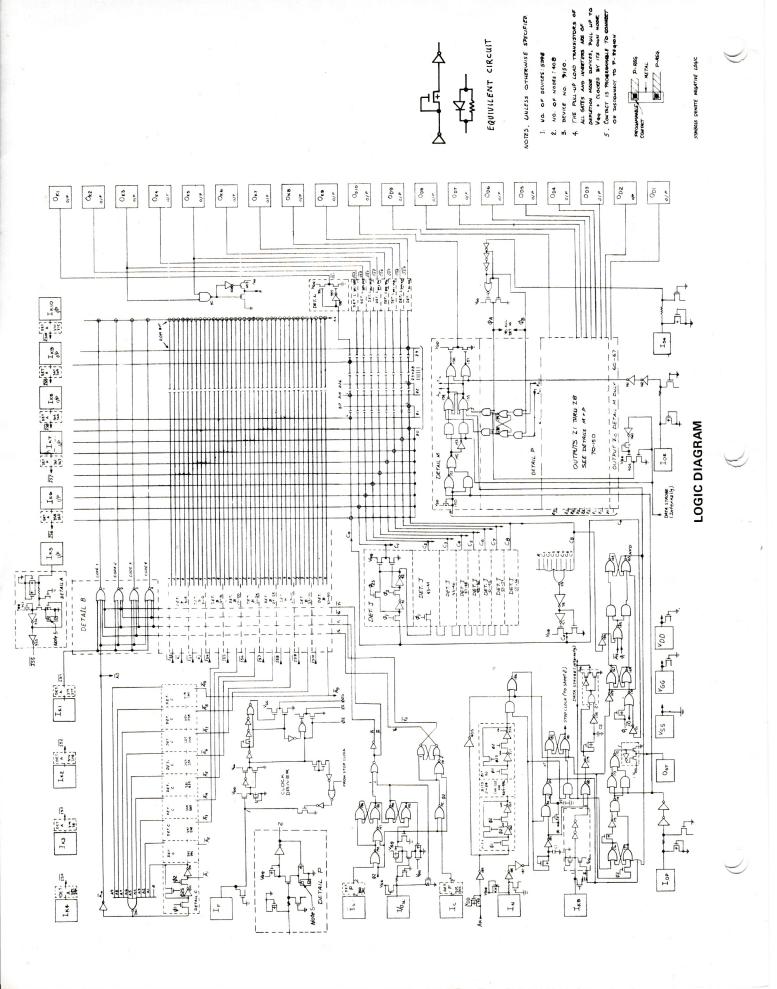

FUNCTIONAL DESCRIPTION: The dynamic keyboard encoder contains input scanning circuitry, ROM Code storage, shift register keyboard state memory, internal clock oscillator, key bounce delay, and an output data register.

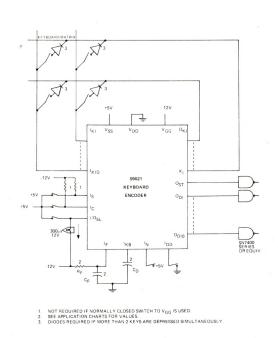

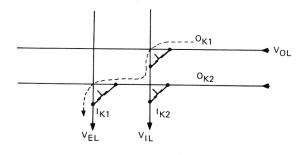

INPUT INTERFACE - HYSTERESIS: All logic and scanning inputs are TTL compatible. Each input contains a 5K $\Omega$  resistor to V<sub>SS</sub> (+5V) to insure adequate V<sub>IH</sub> level. The inputs from the keyboard can be mask programmed to change the input resistance to 15K $\Omega$  to be compatible with the keyboard outputs (O<sub>K</sub>) and provide maximum flexibility for interfacing with various types of keyboard implementations.

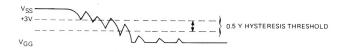

Both logic and keyboard inputs can be mask programmed to exhibit 0.5 volts of hysteresis. Hysteresis causes the inputs to be less sensitive to noise when a transition between logic states is occurring.

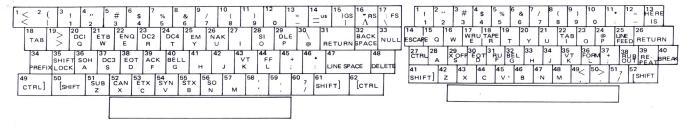

SCANNING AND SWITCH CLOSURE DETECTION: The keyboard switchpoints are arranged in a 9 x 10 matrix. The keys are scanned in time sequence by row and column connections  $(O_K, I_K)$  to the encoder. The encoder clock drives a 9 bit row, and a 10 bit column ring counter. The column counter sequentially interrogates one column input IK per clock period and the row counter sequentially activates one row output (OK) per clock period. The lack of count synchronism (9 bits VS 10 bits) of the counters causes them to sequence thru all possible row-column combinations in 90 clock periods.

A closed cross point switch is detected when the row driver (OK) connected to the switch goes to VOL. If a switch is closed this signal will be transmitted to the column connection (I<sub>K</sub>). If this column input is being interrogated by

MINNEAPOLIS, MINNESOTA 55416 PHONE: (612) 929-6721

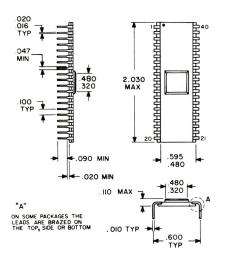

PACKAGE BONDING OPTIONS (Any two may be externally connected) \*\*

- IN\* N Key Rollover/Lockout Select

- I<sub>OP</sub>\* Output logic polarity select

- I<sub>OE</sub> Output enable

- I<sub>SH</sub> Serial data output clock

(\*Options programmed into the S9021)

(\*\*Internal resistors determine logic state when not connected to external pin or bonded to substrate V<sub>SS</sub>)

the encoder the VII signal will be recognized and the encoder will enter the "Key detect" operation mode. All keyboard inputs (IK) have internal resistors to VSS to insure V<sub>IH</sub> signals when column connections are in a floating condition.

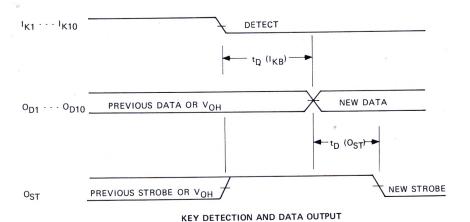

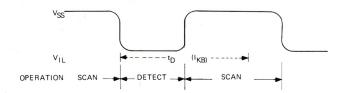

KEY BOUNCE DELAY AND DATA OUTPUT: When a closed switch is detected the scanning clock is stopped and an adjustable time delay is triggered. The input is tested during this delay time. If the switch does not remain stable in the closed position, the encoder resumes scanning. The key bounce delay is adjusted to the desired time delay with an external capacitor.

The ROM is driven by the ring counters. During the key bounce delay period, the outputs of the ROM settle to the output code associated with the state of the ring counters.

At the end of the delay period a pulse is generated if the switch remains closed. This pulse updates the outputs by shifting the output of the ROM into the output register. The output register maintains this new data until a new switch closure is detected and new data is shifted into the register or the encoder detects that no matrix switches are closed.

N KEY LOCKOUT/N KEY ROLLOVER OPERATION: N

key lockout is the capability of depressing two keys in sequence without releasing either of them and getting a coded output only for the first key depressed until it is released. Operation in this mode does not require diodes in the switch matrix if no more than two keys are depressed while the encoder is scanning. N Key lock out operation is achieved by restarting the scanning clock only after a detected switch has been reopened.

N KEY ROLLOVER OPERATION: N Key rollover is the capability of depressing a number of keys in sequence without releasing any of them and getting a coded output for each key in proper sequence. Switch matrix cross points must include a blocking diode when three or more keys are depressed in this mode. N Key rollover operation is achieved by storing the previous state of the switch matrix in a 90 bit shift register. When a closed switch is detected the scan clock stops only if that switch was open during the previous scan cycle. After the key bounce delay has occurred, the clock resumes scanning for other new switch closures.

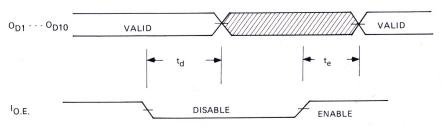

STROBE OPERATION: When the scanning clock stops because of a switch closure, the strobe F/F is reset to the invalid state. At the end of the key bounce delay ROM data is strobed into the output register and the strobe F/F is set. A time delay is built into the propagation of this signal to the output buffer  $(t_d, (O_{ST}))$  to guarantee that data outputs are valid before the strobe output switches

Is, Ic - Shift and Control mode inputs. These inputs select one of four possible output codes. See custom ROM program format and standard pattern keyboard pairings for logic condition - output code relationship. These inputs are ignored when switch closure is detected.

Normally the strobe will stay in the valid state until another

STROBE PULSE OPTION: When operating in the N Key

rollover mode the strobe can be mask programmed to remain

valid for one clock period only. Operating in this mode the

strobe goes valid at the end of the strobe delay, but returns

to the invalid state at the next negative phase two clock

NO KEY DEPRESSED RESET: If the encoder sequences

thru a complete scanning cycle and no switch closures are

detected a reset pulse is generated. This pulse resets the

output data register (OD) to the VOH condition and the

SHIFT LOCK OPERATION: The encoder is put into the

shift mode by either the shift or the shift lock input. A

shift signal applied to the shift lock input locks the key-

board into the shift mode. A shift signal on the shift input

output strobe  $(O_{\mbox{\footnotesize{ST}}})$  to the invalid condition.

switch closure stops the scanning clock.

to the valid state.

unlocks the keyboard.

pulse.

I/OSI - Shift lock input/output. This input/output locks keyboard into the shift mode and provides current output when locked in the shift state. A pulse to VIH sets F/F in shift state.

I<sub>SH</sub> - Serial output shift clock. This input provides clock pulses for shifting data out in the serial output mode.  $V_{IH}$ samples data from adjacent output. Transition to VIII causes sampled data to be shifted toward output ODIO.

$I_N$  - N Key rollover/2 key rollover select input. This input selects the operational mode of the keyboard.  $V_{IL}$ selects N key rollover. VIH selects 2 key rollover. This input can be bonded to an external pin, bonded to VSS, or allowed to float. An internal resistor pulls the input to V<sub>GG</sub> when input is allowed to float.

IOP - Logic polarity select input. This input is used to invert the polarity of the data outputs  $(O_D)$  and the strobe output ( $O_{ST}$ ).  $V_{IH}$  causes  $O_{D}$  and  $O_{ST}$  to function normally. V<sub>II</sub> causes both these signals to be inverted. This input is pulled to  $V_{\mbox{\scriptsize IH}}$  by an internal pullup resistor when allowed to float.

Io.E. - Output enable. This input enables the data outputs.  $V_{IH}$  enables.  $V_{IL}$  disables. This input goes to  $V_{IH}$ when allowed to float.

O<sub>K1</sub> - O<sub>K9</sub> - Keyboard switch matrix driver outputs. A VOL signal is presented on each scanning output in time sequence controlled by the internal clock. These signals provide a scanning input to the keyboard switch matrix.  $O_{D1} - O_{D10}$  — Ten Bit data output. These outputs are updated from the ROM each time a switch closure is detected. A VOH or VOL signal is programmed to appear on these outputs by referring to the ROM programming format. OST - Output Data Strobe. A VOH signal indicates that data outputs are invalid. A VOI signal indicates valid data. The logic states can be reversed by the IOP input.

**FUNCTIONAL DIAGRAM**

IK1 - IK10 - Inputs from keyboard switch matrix. Switch closures in the keyboard matrix are detected by sampling these inputs. A VIH indicates an open switch. A VIL indicates a closed switch.

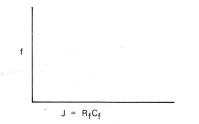

1<sub>F</sub> - Internal oscillator frequency adjust input. This input determines encoder scanning frequency. External connection of an RC network as shown in the electrical connection diagram determines the frequency of the internal clock. Refer to plot of frequency VS time constant for resistance and capacitance values. This input may also be driven by an external clock for precise synchronization and control.

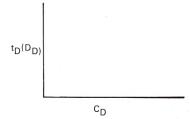

1<sub>KB</sub> - Keybounce delay adjust input. This input adjusts input sample pulse width. External connection of a capacitor as shown in the connection diagram determines key bounce delay. Refer to plot of capacitance VS time delay for appropriate capacitance values.

Positive voltage on any pin Negative voltage on any pin Storage and Operating Chip Temperature  $V_{SS} + 0.3V$   $V_{SS} - 22 V$  $0^{\circ}$  to +  $70^{\circ}$ C

Specifications (T<sub>A</sub> =  $0^{\circ}$  to +  $70^{\circ}$ C,  $V_{SS}$  = + 5V  $\pm$  5%,  $V_{DD}$  = GROUND,  $V_{GG}$  = - 12V  $\pm$  5%)

|                                   |                                      | MIN.                  | MAX.                  | UNITS      | CONDITIONS                                           |

|-----------------------------------|--------------------------------------|-----------------------|-----------------------|------------|------------------------------------------------------|

| v <sub>IH</sub>                   | Logic input high level               | V <sub>SS</sub> - 1.0 | $V_{SS}$              | Volts      | Internal 5 K $\Omega$ to V <sub>SS</sub> establishes |

| VIL                               | Logic input low level                | $v_{GG}$              | V <sub>SS</sub> - 4.3 | Volts      | this level on all inputs except $I_N$ and $I/O_{SL}$ |

| V <sub>OH</sub>                   | Logic output high level              | V <sub>SS</sub> - 0.5 | $v_{SS}$              | Volts      | ΙΟ = 100 μα                                          |

| VOL                               | Logic output low level               |                       | +0.4                  | Volts      | I <sub>O</sub> = - 1.6 ma                            |

| f<br>(                            | Clock operating frequency range      | 10                    | 200                   | кнг        |                                                      |

| $\triangle f_{t}$                 | Oscillator temperature drift         |                       | 2                     | %          |                                                      |

| tD (IKB)                          | Adjustable range of key bounce delay | 0.1                   | 5                     | ms         |                                                      |

| t <sub>r</sub> (O <sub>ST</sub> ) | Data strobe rise time                |                       | 300                   | ns         | Load = 50 pf, 1 TTL input                            |

| t <sub>D</sub> (O <sub>ST</sub> ) | Data to strobe output delay          |                       |                       | ns         |                                                      |

| t <sub>r</sub> (O <sub>D</sub> )  | Data output rise time                |                       | 1.0                   | $\mu$ s    | Load = 50 pf, 1 TTL input                            |

| t <sub>e</sub> (O <sub>OE</sub> ) | Output Enable time                   |                       |                       | ns         |                                                      |

| t <sub>d</sub> (O <sub>OE</sub> ) | Output Disable time                  |                       |                       | ns         |                                                      |

| CIN                               | Input capacitance                    |                       | 10                    | pf         | $V_{IN} = OV, f = 1 MHZ$                             |

| COUT                              | Output capacitance                   |                       | 10                    | pf         | $V_{OUT} = -OV$ , f = 1 MHZ                          |

| I <sub>SS</sub>                   | V <sub>SS</sub> supply current       |                       |                       | ma         |                                                      |

| 1 <sub>DD</sub>                   | V <sub>DD</sub> supply current       |                       |                       | ma         |                                                      |

| l <sub>GG</sub>                   | V <sub>GG</sub> supply current       |                       |                       | ma         |                                                      |

| $R_c$                             | Switch contact resistance            |                       | 3                     | k $\Omega$ | (3mb)                                                |

| R <sub>op</sub>                   | Switch open resistance               | 500                   |                       | k $\Omega$ |                                                      |

OUTPUT DISABLE

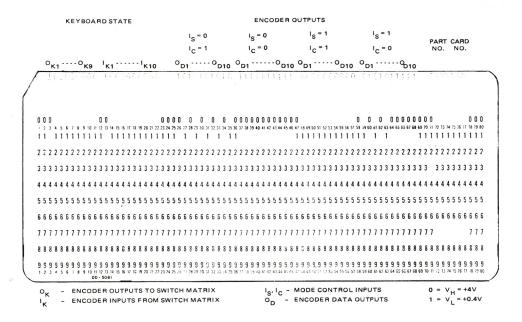

CUSTOM ROM PROGRAM FORMAT: The Dynamic Keyboard is most accurately and economically programmed by submitting a deck of 91 punched cards. The adjoining illustration shows a typical card and defines the card location of all input information. Each card contains information indicating output code for each of the 4 operational modes at a key matrix location. Columns 3 - 11 on the card indicate the state of the encoder outputs to the switch matrix and Columns 13 - 22 indicate the state of the encoder inputs from switch matrix. Columns 26 - 35 contain desired data outputs when mode control inputs are  $I_S = 0$ ,  $I_C = 1$ . Columns 37 - 68 contain data outputs for the other 3 keyboard modes. Columns 71 - 75 contain a part number which is assigned by AMI and inserted by the customer. Columns 77 - 78 contain the card number (0 through 90).

Keyboard matrix locations are assigned to card numbers in the following sequence:

card 80 - 89;  $O_{K9}$ ,  $I_{K1}$  thru  $I_{K10}$

The last card in the deck (90) determines which mask programmable logic options are selected. A "1" in column 10 converts the static output strobe to a pulse, A "1" in column 20 inserts hysteresis in the  $I_K$  inputs. A "1" in column 30 converts ( $I_K$ ) input pullup resistors (to  $V_{SS}$ ) from MOS compatibility (15k $\Omega$ ) to TTL compatibility (5k $\Omega$ ).

USASCII TELETYPEWRITER 63 KEY - 3 LEVEL

USASCII TELETYPEWRITER 53 KEY - 3 LEVEL OR 4 LEVEL

## **S9021 KEYBOARD APPLICATIONS**

|                 | lK1 |      |     | . — . |     |     |     |              | _   |     | _  |    |      |     |    |     |    |     |     | <sup>I</sup> K10 |

|-----------------|-----|------|-----|-------|-----|-----|-----|--------------|-----|-----|----|----|------|-----|----|-----|----|-----|-----|------------------|

| 0 <sub>K1</sub> | 1   | !    | 2   | ,,    | 3   | #   | 4   | \$           | 5   | %   | 6  | &  | 7    | ,   | 8  | (   | 9  | )   | 0   | 0                |

| I               | 1   | !    | 2   | "     | 3   | #   | 4   | \$           | 5   | %   | 6  | &  | 7    | ,   | 8  | (   | 9  | )   | 0   | 0                |

|                 | Q   | Q    | W   | W     | Е   | Е   | R   | R            | Т   | Т   | Υ  | Υ  | U    | U   | ı  | 1   | OH | -   | Р   | @                |

|                 | DC1 | DC1  | ЕТВ | ETB   | ENQ | ENQ | DC2 | DC2          | DC4 | DC4 | EM | EM | NAK  | NAK | нт | нт  | SI | US  | DLE | NUL              |

| 1               | А   | А    | S   | S     | Ď   | D   | F   | F            | G   | G   | Н  | Н  | J    | J   | K  | [   | L  | \   | ;   | +                |

| 1               | SOH | SOH  | DC3 | DC3   | EOT | EOT | ACK | ACK          | BEL | BEL | BS | BS | LF   | LF  | VT | ESC | FF | FS  | ;   | +                |

| i               | Z   | Z    | Х   | Χ     | С   | С   | ٧   | $^{\prime}V$ | В   | В   | N  |    | М    | ]   | ,  | <   | •  | >   | /   | ?                |

| l<br>I          | SUB | SUB  | CAN | CAN   | ETX | ETX | SYN | SYN          | STX | STX | SO | RS | CR   | GS  | ,  | <   |    | >   | /   | ?                |

| 1               |     | <    |     |       | SI  |     | ES  | 0            |     | ) C | :  | *  | _    | =   |    | _F  |    | CR  | DI  | _                |

| i               | NU  | JL   | NU  | J.L.  | 51  |     | E 5 |              |     | 3S  | :  |    | _    |     |    |     |    | , n | Di  |                  |

| 1 * /           |     | 1 .  | 2   | 2     | 3   |     | 4   | +            | !   | 5   |    | 6  |      | 7   |    | 8   |    | 9   | @   | \                |

| 1               |     |      |     |       |     |     |     |              |     |     |    |    |      |     |    |     |    |     | NL  | J L              |

| i               | 1   | !    | 2   | "     | 3   | #   | 4   | \$           | 5   | %   | 6  | &  | 7    |     | 8  | (   | О  | 0   | р   | Р                |

|                 | Nι  | JL - | N   | JL    | NU  | IL  | NU  | L            | NU  | JL  | NU | JL | NU   | JL  | N  | JL  | S  |     | DE  | L                |

| i               | 9   | )    | 0   | NUL   | -   | =   |     |              | /   | ?   | ;  | +  | :    | *   | k  | K   | 1  | L   | >   | >                |

| !<br>!          | N   | JL   | N   | UL    | NU  | IL  | DL  | .E           | N   | UL  | N  | JL | " NU | JL  | ١  | /T  | F  | F   | NU  | L                |

| į               | [   |      | _   |       | ]   |     | ,   | ,            |     |     | n  | N  | m    | м   | ^  | ~   | \  | :   |     |                  |

| 0 <sub>K9</sub> | ES  | SC . | U   | IS    | G   | S   | NU  | JL           | N   | UL  | S  | 0  | С    | R   | F  | RS  | FS | 5   | H.  | Г                |

| - 1 |   |    |    |   |                             | S              | С     |

|-----|---|----|----|---|-----------------------------|----------------|-------|

|     | N | S  | N  | _ | Unshifted                   | VH             | $v_H$ |

|     | _ |    | S  | _ | Shift depressed             | V <sub>I</sub> | Vн    |

|     | C | SC | С  | _ | Control depressed           | ٧H             | ٧ï    |

| 1   |   | ~  | SC | _ | Shift and control depressed | v.             | ٧Ĺ    |

|     |   |    |    |   | 1                           | _              | _     |

<sup>\*</sup> Individual digit keys for separate numeric capability.

## **KEYBOARD PAIRINGS FOR S9021**

|      |                |                     |                   |   |    | $O_{D7}$         | = | U6 (CAPS + SMALL)         |

|------|----------------|---------------------|-------------------|---|----|------------------|---|---------------------------|

|      |                | o <sub>D1</sub> = 0 | 1 0 <sub>D4</sub> | = | U4 | $o_{D8}$         | = | U7                        |

| USAS | SASCII OUTPUTS | o <sub>D2</sub> = 0 | o <sub>D5</sub>   | = | U5 | $o_{D9}$         | = | ODD PARITY                |

|      |                | o <sub>D3</sub> = U | 3 O <sub>D6</sub> | = | U6 | O <sub>D10</sub> | = | ODD PARITY (CAPS + SMALL) |

#### APPLICATION INFORMATION

Diodes at crosspoints: Diodes are required at crosspoints if more than three keys may be depressed at once. Diodes prevent a false signal on  $I_{K1}$  when  $V_{OL}$  is applied to  $O_{K1}$  as shown below.

**KEYBOARD SWITCH MATRIX**

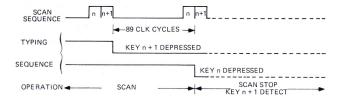

**BURST RATE TYPING:** When keys are depressed in rapid sequence care must be taken to insure that output codes are generated in the proper order.

#### N KEY ROLLOVER MODE:

# MINIMUM TIME BETWEEN KEY DEPRESSIONS

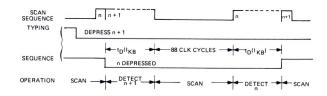

The worst case for N Key rollover is when three adjacent keys are depressed in reverse scan sequence (n+1, n, n-1). If key n is depressed when key n+1 is being detected, then key n-1 must not be depressed before a time delay of 88 clock cycles plus the key bounce delay or the keys will not generate output codes in the proper sequence. The clock frequency and bounce delay may be adjusted within their allowable ranges to achieve a minimum time between key depressions as little as 0.5 milliseconds or as high as 14 milliseconds.

**N KEY LOCKOUT MODE:** The worst case occurs when two keys that are adjacent to each other in the scanning sequence (scanning sequence is Key n, Key n-1) are depressed in reverse order (typing sequence is Key n+1, Key n).

### MINIMUM TIME BETWEEN KEY DEPRESSIONS

If key n + 1 has just been interrogated before the key is depressed the scanning clock must go thru 90 clock cycles before key n + 1 is detected. Key n may not be depressed until after the 89th clock cycle or it will be detected first by the encoder. The clock frequency can be adjusted to provide a minimum key depression interval as low as 0.5 milliseconds or as high as 9 milliseconds.

**SKIPPING A KEY:** In the N key lockout mode a key must remain in a depressed state after another key is released to be recognized as shown in the figure. This time may be varied by clock frequency and key bounce delay from 0.5 to 14 milliseconds.

MINIMUM SWITCH RELEASE TIME

In the N Key rollover mode a key must remain in a depressed state as shown in the Figure.

## MINIMUM SWITCH CLOSURE TIME

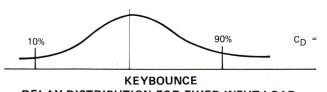

**KEY BOUNCE**: A typical switch closure with contact bounce is shown in the Figure.

SWITCH CLOSURE INPUT

Hysteresis on the inputs reduces the chance of the contact bounce causing the encoder to malfunction. When the voltage reaches the lower hysteresis threshold, the threshold shifts upward thus eliminating any oscillations that might occur on the output of the input sensing circuitry if the input voltage recrosses the initial threshold voltage. The threshold typically ranges around 3 volts.

**NOISE ON INPUT**

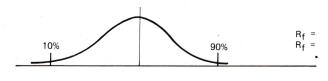

FREQUENCY DISTRIBUTION FOR FIXED INPUT LOAD

INPUT NOISE: The key bounce delay further limits the chance of keyboard malfunction because of key bounce or spurious noise pulses. If an input has a noise disturbance that is strong enough to cause the input to make a logic transition, the encoder may detect a switch closure. The key bounce delay eliminates the possibility of an output code being generated by requiring a detected input to stay negative during the delay period or no output code and strobe is generated.

This type of noise may be capacitance coupled on keyboard interconnect lines or may be caused by low frequency key bounce.

**DELAY DISTRIBUTION FOR FIXED INPUT LOAD**

**CLOCK FREQUENCY VS INPUT LOAD**

**KEYBOUNCE DELAY VS INPUT LOAD**

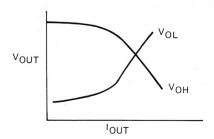

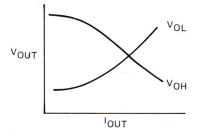

DATA OUTPUT CHARACTERISTIC

**KEYBOARD OUTPUT CHARACTERISTIC**

Devices sold by AMI are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale. AMI makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the reserves the right to change specifications and prices at any time and without notice.

and without notice.

A DIVISION OF AMERICAN MICRO-SYSTEMS, INC.

3800 Homestead Road Santa Clara, Calif. 95051 (408) 246-0330 TWX 910-338-0018