# EMBEDDED SoPC DESIGN WITH NIOS II PROCESSOR AND VERILOG EXAMPLES

# EMBEDDED SoPC DESIGN WITH NIOS II PROCESSOR AND VERILOG EXAMPLES

Pong P. Chu Cleveland State University

Copyright © 2012 by John Wiley & Sons, Inc. All rights reserved

Published by John Wiley & Sons, Inc., Hoboken, New Jersey Published simultaneously in Canada

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning, or otherwise, except as permitted under Section 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923, (978) 750-8400, fax (978) 750-4470, or on the web at www.copyright.com. Requests to the Publisher for permission should be addressed to the Permissions Department, John Wiley & Sons, Inc., 111 River Street, Hoboken, NJ 07030, (201) 748-6011, fax (201) 748-6008, or online at http://www.wiley.com/go/permission.

Limit of Liability/Disclaimer of Warranty: While the publisher and author have used their best efforts in preparing this book, they make no representations or warranties with respect to the accuracy or completeness of the contents of this book and specifically disclaim any implied warranties of merchantability or fitness for a particular purpose. No warranty may be created or extended by sales representatives or written sales materials. The advice and strategies contained herein may not be suitable for your situation. You should consult with a professional where appropriate. Neither the publisher nor author shall be liable for any loss of profit or any other commercial damages, including but not limited to special, incidental, consequential, or other damages.

For general information on our other products and services or for technical support, please contact our Customer Care Department within the United States at (800) 762-2974, outside the United States at (317) 572-3993 or fax (317) 572-4002.

Wiley also publishes its books in a variety of electronic formats. Some content that appears in print may not be available in electronic formats. For more information about Wiley products, visit our web site at www.wiley.com.

#### Library of Congress Cataloging-in-Publication Data:

```

Chu, Pong P., 1959–

Embedded SoPC design with NIOS II processor and Verilog examples / Pong P. Chu.

p. cm.

Includes bibliographical references and index.

ISBN 978-1-118-01103-4 (hardback)

1. Embedded computer systems. 2. Field programmable gate arrays. 3. Verilog (Computer hardware description

language) 1. Title.

TK7895.E42C48 2012

006.2'2---dc23 2011048946

Printed in the United States of America.

```

10 9 8 7 6 5 4 3 2 1

To my mother, Chi-Te, my wife, Lee, and my daughter, Patricia

# CONTENTS

| Pr | eface                       |                                          | xxvii  |

|----|-----------------------------|------------------------------------------|--------|

| A  | know                        | vledgments                               | xxxiii |

| 1  | Overview of Embedded System |                                          |        |

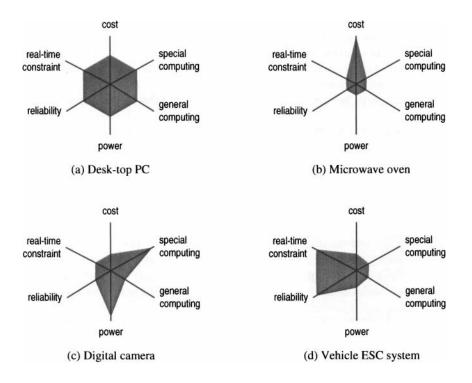

|    | 1.1                         | Introduction                             | 1      |

|    |                             | 1.1.1 Definition of an embedded system   | 1      |

|    |                             | 1.1.2 Example systems                    | 2      |

|    | 1.2                         | System design requirements               | 3      |

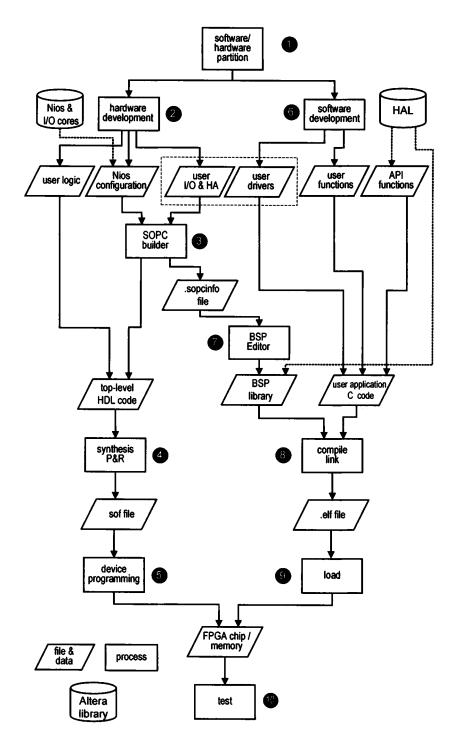

|    | 1.3                         | Embedded SoPC systems                    | 4      |

|    |                             | 1.3.1 Basic development flow             | 5      |

|    | 1.4                         | Book organization                        | 8      |

|    | 1.5                         | Bibliographic notes                      | 8      |

|    |                             | PART I BASIC DIGITAL CIRCUITS DEVELOPMEN | т      |

| 2  | Gate                        | e-level Combinational Circuit            | 11     |

|    | 2.1                         | Introduction                             | 11     |

|    | 2.2                         | General description                      | 12     |

|    | 2.3                         | Basic lexical elements and data types    | 13     |

|    |                             | 2.3.1 Lexical elements                   | 13     |

|    | 2.4                         | Data types                               | 14     |

# www.it-ebooks.info

vii

|   |      | 2.4.1    | Four-value system                                 | 14 |

|---|------|----------|---------------------------------------------------|----|

|   |      | 2.4.2    | Data type groups                                  | 14 |

|   |      | 2.4.3    | Number representation                             | 14 |

|   |      | 2.4.4    | Operators                                         | 16 |

|   | 2.5  | Program  | m skeleton                                        | 16 |

|   |      | 2.5.1    | Port declaration                                  | 16 |

|   |      | 2.5.2    | Program body                                      | 17 |

|   |      | 2.5.3    | Signal declaration                                | 18 |

|   |      | 2.5.4    | Another example                                   | 18 |

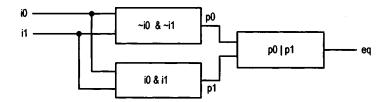

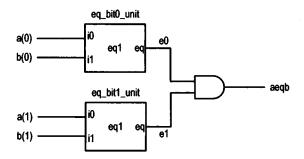

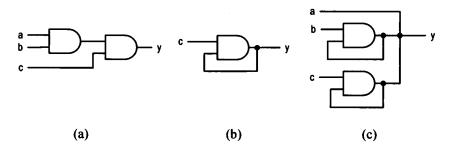

|   | 2.6  | Structu  | ral description                                   | 19 |

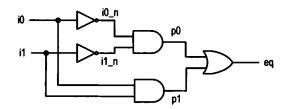

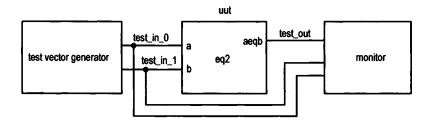

|   | 2.7  | Testber  | nch                                               | 22 |

|   | 2.8  | -        | raphic notes                                      | 23 |

|   | 2.9  | Suggest  | ted experiments                                   | 24 |

|   |      | 2.9.1    | Code for gate-level greater-than circuit          | 24 |

|   |      | 2.9.2    | Code for gate-level binary decoder                | 24 |

| 3 | Ove  | rview of | FPGA and EDA Software                             | 25 |

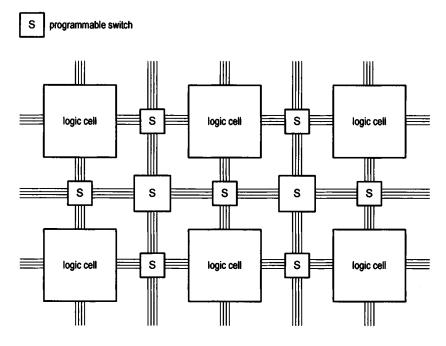

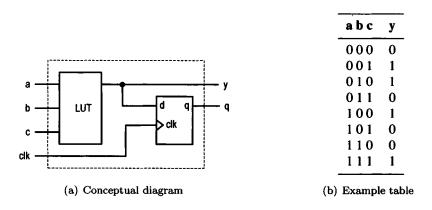

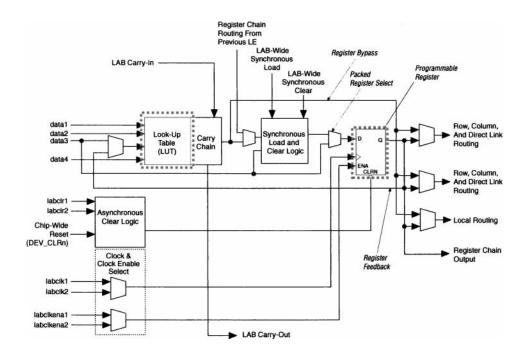

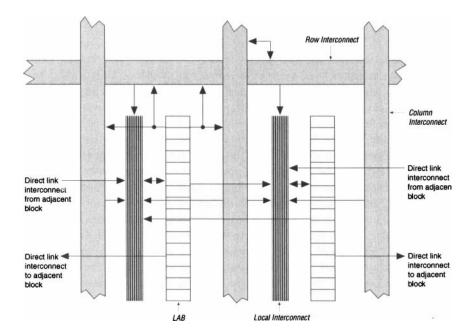

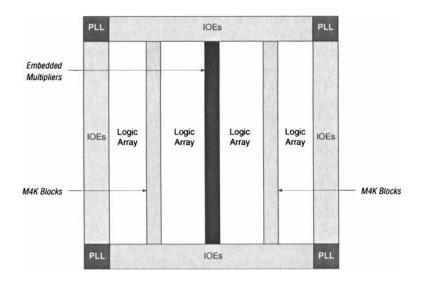

|   | 3.1  | FPGA     |                                                   | 25 |

|   |      | 3.1.1    | Overview of a general FPGA device                 | 25 |

|   |      | 3.1.2    | Overview of the Altera Cyclone II devices         | 27 |

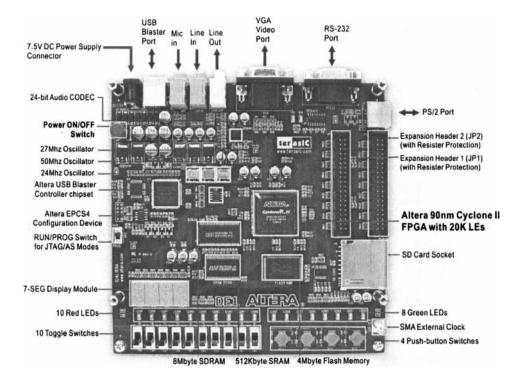

|   | 3.2  | Overvie  | ew of the Altera DE1 and DE2 boards               | 30 |

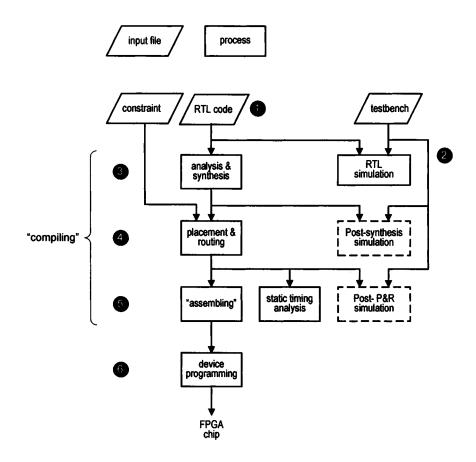

|   | 3.3  | Develo   | pment flow                                        | 30 |

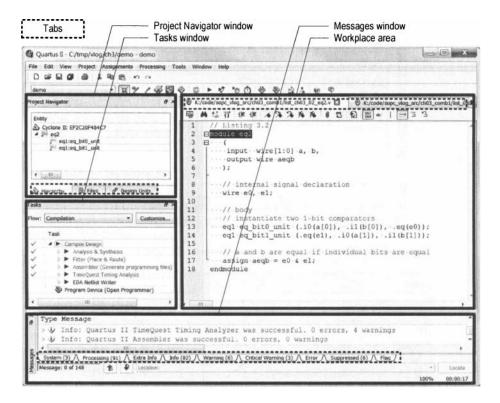

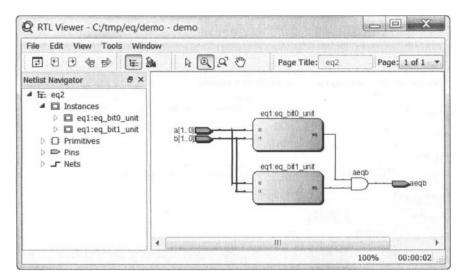

|   | 3.4  | Overvie  | ew of Quartus II                                  | 33 |

|   | 3.5  | Short t  | utorial of Quartus II                             | 35 |

|   |      | 3.5.1    | Create the design project                         | 36 |

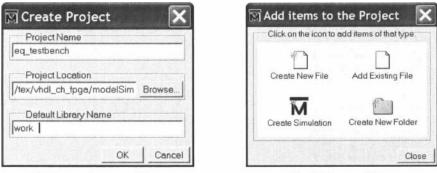

|   |      | 3.5.2    | Create a testbench and perform the RTL simulation | 41 |

|   |      | 3.5.3    | Compile the project                               | 41 |

|   |      | 3.5.4    | Perform timing analysis                           | 43 |

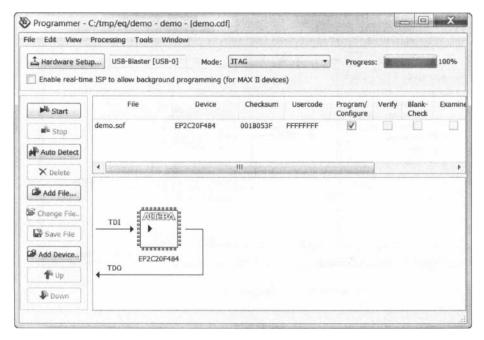

|   |      | 3.5.5    | Program the FPGA device                           | 43 |

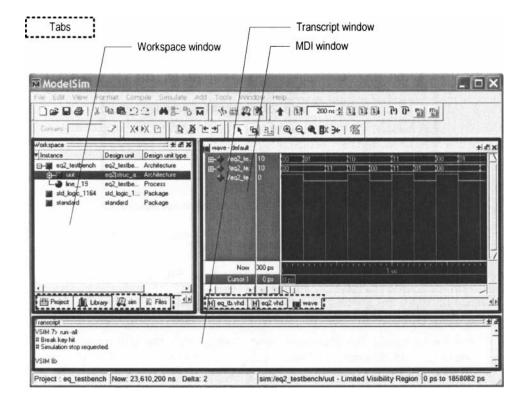

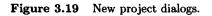

|   | 3.6  |          | utorial on the ModelSim HDL simulator             | 45 |

|   | 3.7  | -        | raphic notes                                      | 50 |

|   | 3.8  |          | ted experiments                                   | 50 |

|   |      | 3.8.1    | Gate-level greater-than circuit                   | 50 |

|   |      | 3.8.2    | Gate-level binary decoder                         | 51 |

| 4 | RT-I | evel Cor | mbinational Circuit                               | 53 |

|   | 4.1  | Operate  | ors                                               | 53 |

|   |      | 4.1.1    | Arithmetic operators                              | 55 |

|   |      | 4.1.2    | Shift operators                                   | 55 |

|   |      | 4.1.3    | Relational and equality operators                 | 56 |

|   |      | 4.1.4    | Bitwise, reduction, and logical operators         | 56 |

|   |      |          |                                                   |    |

|      | 4.1.5    | Concatenation and replication operators              | 57 |

|------|----------|------------------------------------------------------|----|

|      | 4.1.6    | Conditional operators                                | 58 |

|      | 4.1.7    | Operator precedence                                  | 59 |

|      | 4.1.8    | Expression bit-length adjustment                     | 59 |

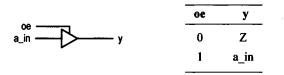

|      | 4.1.9    | Synthesis of $z$ and $x$ values                      | 60 |

| 4.2  | Always   | block for a combinational circuit                    | 62 |

|      | 4.2.1    | Basic syntax and behavior                            | 62 |

|      | 4.2.2    | Procedural assignment                                | 63 |

|      | 4.2.3    | Variable data types                                  | 63 |

|      | 4.2.4    | Simple examples                                      | 64 |

| 4.3  | If state | ment                                                 | 65 |

|      | 4.3.1    | Syntax                                               | 65 |

|      | 4.3.2    | Examples                                             | 66 |

| 4.4  | Case sta | atement                                              | 68 |

|      | 4.4.1    | Syntax                                               | 68 |

|      | 4.4.2    | Examples                                             | 69 |

|      | 4.4.3    | The casez and casex statements                       | 69 |

|      | 4.4.4    | Full case and parallel case                          | 70 |

| 4.5  | Routing  | g structure of conditional control constructs        | 71 |

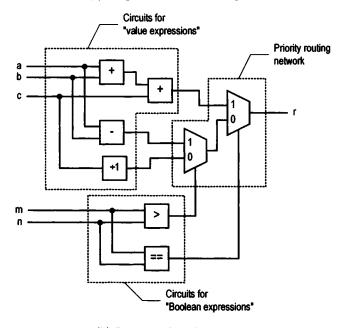

|      | 4.5.1    | Priority routing network                             | 71 |

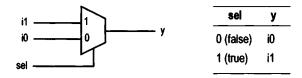

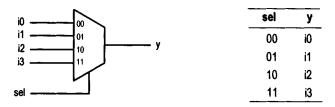

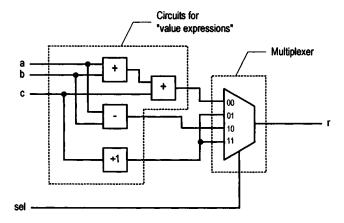

|      | 4.5.2    | Multiplexing network                                 | 73 |

| 4.6  | General  | l coding guidelines for an always block              | 74 |

|      | 4.6.1    | Common errors in combinational circuit codes         | 74 |

|      | 4.6.2    | Guidelines                                           | 77 |

| 4.7  | Parame   | ter and constant                                     | 78 |

|      | 4.7.1    | Constant                                             | 78 |

|      | 4.7.2    | Parameter                                            | 79 |

|      | 4.7.3    | Use of parameters in Verilog-1995                    | 81 |

| 4.8  | Design   | examples                                             | 81 |

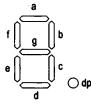

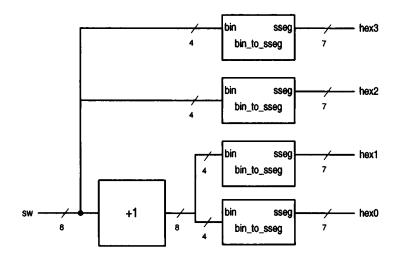

|      | 4.8.1    | Hexadecimal digit to seven-segment LED decoder       | 81 |

|      | 4.8.2    | Sign-magnitude adder                                 | 83 |

|      | 4.8.3    | Barrel shifter                                       | 85 |

|      | 4.8.4    | Simplified floating-point adder                      | 87 |

| 4.9  | Bibliog  | raphic notes                                         | 90 |

| 4.10 | Suggest  | ed experiments                                       | 91 |

|      | 4.10.1   | Multifunction barrel shifter                         | 91 |

|      | 4.10.2   | Dual-priority encoder                                | 91 |

|      | 4.10.3   | BCD incrementor                                      | 91 |

|      | 4.10.4   | Floating-point greater-than circuit                  | 92 |

|      | 4.10.5   | Floating-point and signed integer conversion circuit | 92 |

|      | 4.10.6   | Enhanced floating-point adder                        | 92 |

| 5 | Reg | ular Seq     | uential Circuit                                      | 93  |

|---|-----|--------------|------------------------------------------------------|-----|

|   | 5.1 | Introduction |                                                      |     |

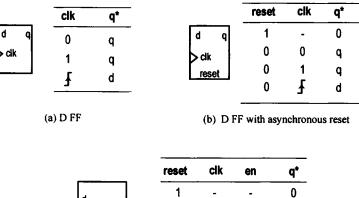

|   |     | 5.1.1        | D FF and register                                    | 94  |

|   |     | 5.1.2        | Synchronous system                                   | 94  |

|   |     | 5.1.3        | Code development                                     | 95  |

|   | 5.2 | HDL c        | ode of the FF and register                           | 95  |

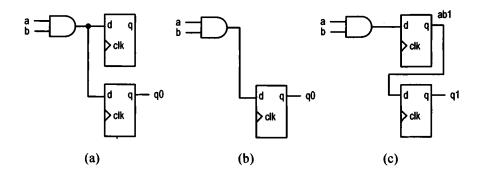

|   |     | 5.2.1        | D FF                                                 | 96  |

|   |     | 5.2.2        | Register                                             | 99  |

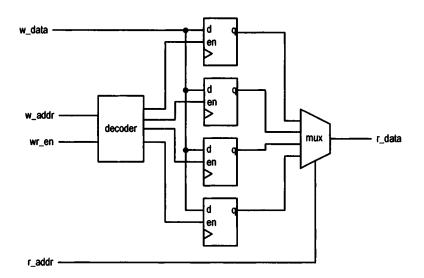

|   |     | 5.2.3        | Register file                                        | 99  |

|   |     | 5.2.4        | SRAM                                                 | 102 |

|   | 5.3 | Simple       | design examples                                      | 103 |

|   |     | 5.3.1        | Shift register                                       | 103 |

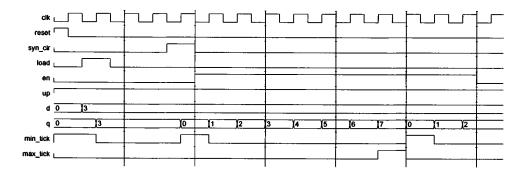

|   |     | 5.3.2        | Binary counter and variant                           | 104 |

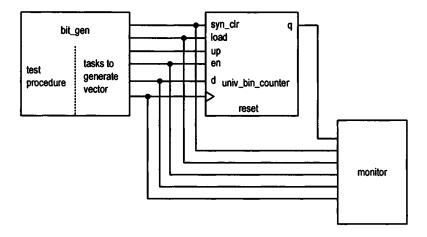

|   | 5.4 | Testbe       | nch for sequential circuits                          | 107 |

|   | 5.5 | Timing       | g analysis                                           | 110 |

|   |     | 5.5.1        | Timing parameters                                    | 110 |

|   |     | 5.5.2        | Timing considerations in Quartus II                  | 112 |

|   | 5.6 | Case st      | tudy                                                 | 114 |

|   |     | 5.6.1        | Stopwatch                                            | 114 |

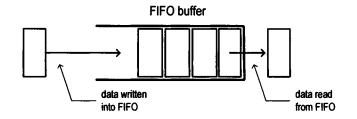

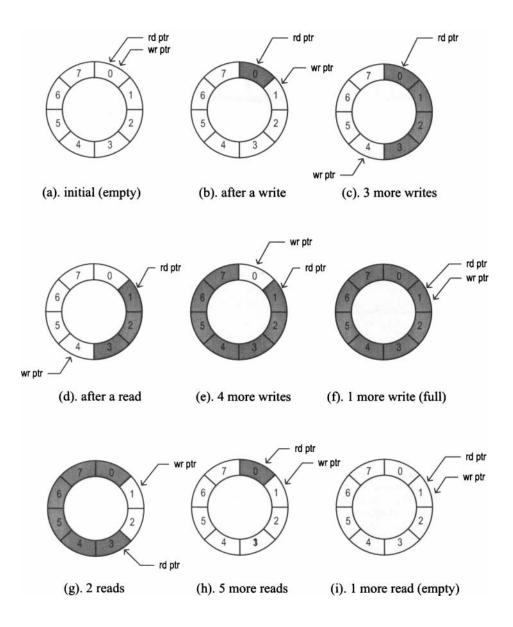

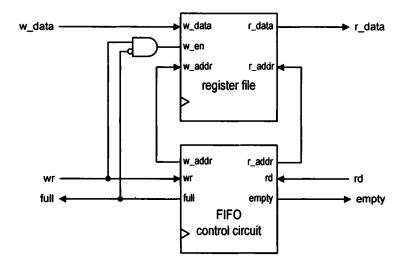

|   |     | 5.6.2        | FIFO buffer                                          | 117 |

|   | 5.7 | Cyclon       | e II device embedded memory module                   | 121 |

|   |     | 5.7.1        | Overview of memory options of DE1 board              | 121 |

|   |     | 5.7.2        | Overview of embedded M4K module                      | 122 |

|   |     | 5.7.3        | Methods to incorporate embedded memory module        | 122 |

|   |     | 5.7.4        | HDL module to infer synchronous single-port RAM      | 124 |

|   |     | 5.7.5        | HDL module to infer synchronous simple dual-port RAM | 126 |

|   |     | 5.7.6        | HDL module to infer synchronous true dual-port RAM   | 127 |

|   |     | 5.7.7        | HDL module to infer synchronous ROM                  | 129 |

|   |     | 5.7.8        | HDL module to specify RAM initial values             | 130 |

|   |     | 5.7.9        | FIFO buffer revisited                                | 131 |

|   | 5.8 | Bibliog      | raphic notes                                         | 132 |

|   | 5.9 | Sugges       | ted experiments                                      | 132 |

|   |     | 5.9.1        | Programmable square-wave generator                   | 132 |

|   |     | 5.9.2        | Pulse width modulation circuit                       | 133 |

|   |     | 5.9.3        | Rotating square circuit                              | 133 |

|   |     | 5.9.4        | Heartbeat circuit                                    | 133 |

|   |     | 5.9.5        | Rotating LED banner circuit                          | 134 |

|   |     | 5.9.6        | Enhanced stopwatch                                   | 134 |

|   |     | 5.9.7        | FIFO with data width conversion                      | 134 |

|   |     | 5.9.8        | Stack                                                | 134 |

|   |     | 5.9.9        | ROM-based sign-magnitude adder                       | 134 |

|   |     | 5.9.10       | ROM-based temperature conversion                     | 135 |

| 6 | FSM | 1      |                                                     | 137 |

|---|-----|--------|-----------------------------------------------------|-----|

|   | 6.1 | Introd | uction                                              | 137 |

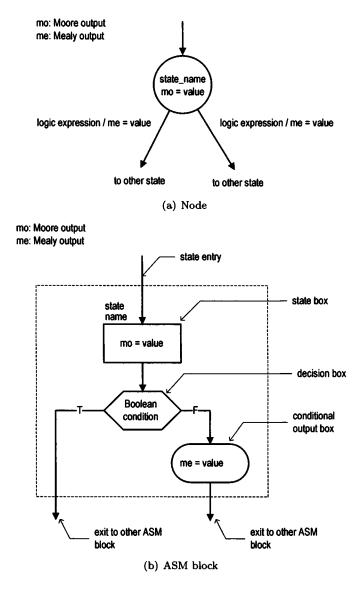

|   |     | 6.1.1  | Mealy and Moore outputs                             | 138 |

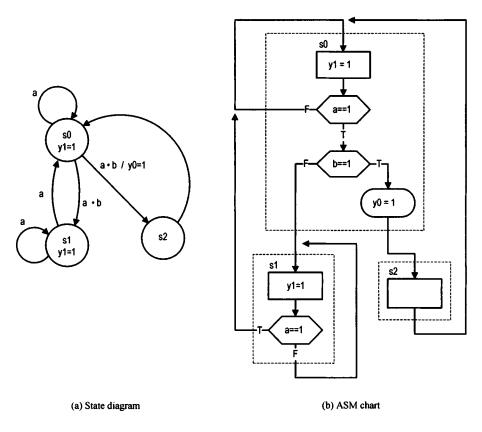

|   |     | 6.1.2  | FSM representation                                  | 138 |

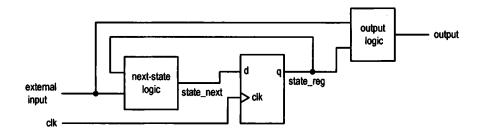

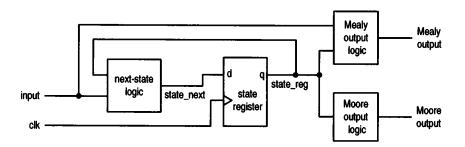

|   | 6.2 | FSM o  | code development                                    | 140 |

|   | 6.3 | Design | n examples .                                        | 143 |

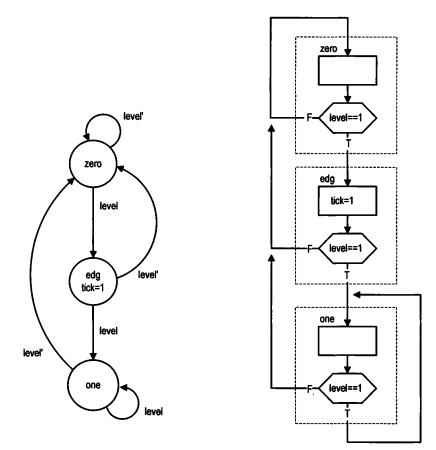

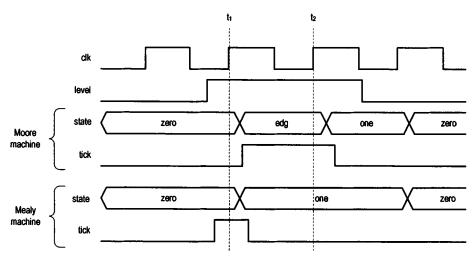

|   |     | 6.3.1  | Rising-edge detector                                | 143 |

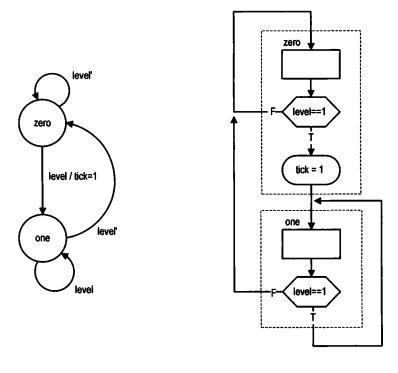

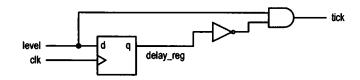

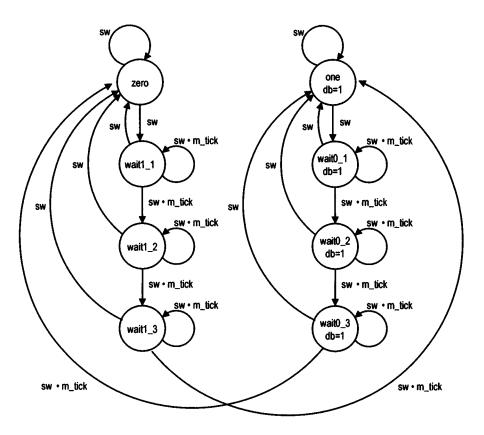

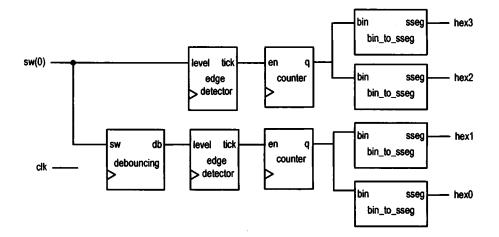

|   |     | 6.3.2  | Debouncing circuit                                  | 147 |

|   |     | 6.3.3  | Testing circuit                                     | 151 |

|   | 6.4 | Biblio | graphic notes                                       | 153 |

|   | 6.5 | Sugges | sted experiments                                    | 153 |

|   |     | 6.5.1  | Dual-edge detector                                  | 153 |

|   |     | 6.5.2  | Alternative debouncing circuit                      | 153 |

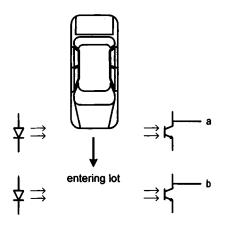

|   |     | 6.5.3  | Parking lot occupancy counter                       | 153 |

| 7 | FSN | 1D     |                                                     | 155 |

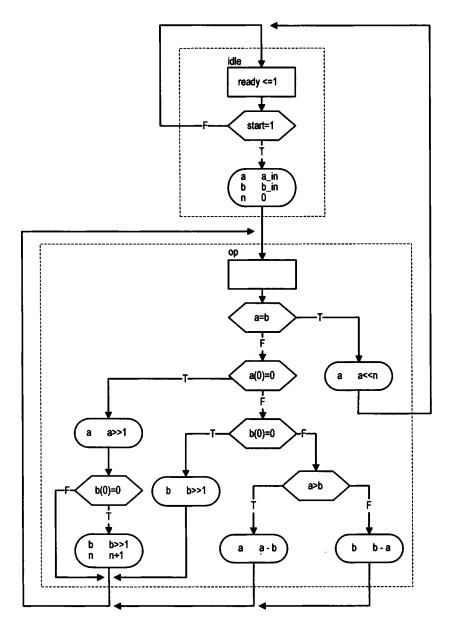

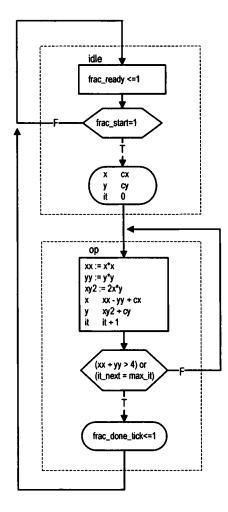

|   | 7.1 | Introd | uction                                              | 155 |

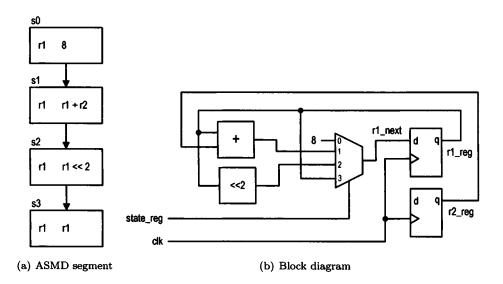

|   |     | 7.1.1  | Single RT operation                                 | 156 |

|   |     | 7.1.2  | ASMD chart                                          | 156 |

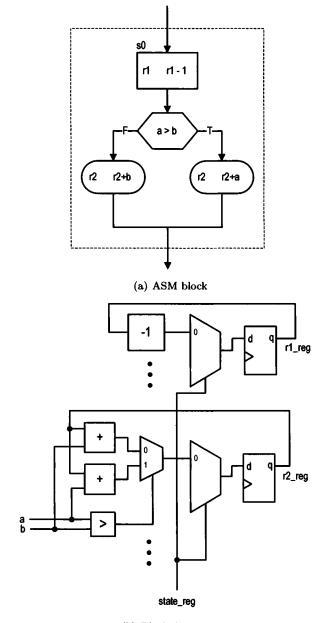

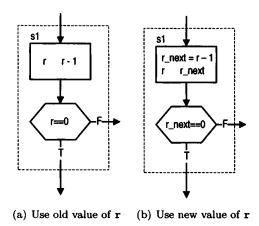

|   |     | 7.1.3  | Decision box with a register                        | 158 |

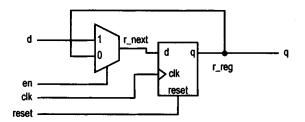

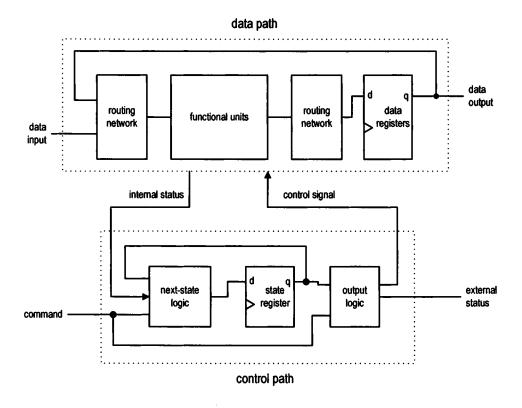

|   | 7.2 | Code   | development of an FSMD                              | 161 |

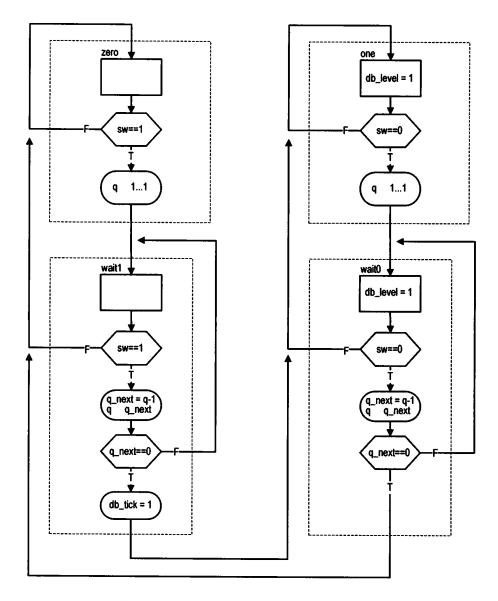

|   |     | 7.2.1  | Debouncing circuit based on RT methodology          | 161 |

|   |     | 7.2.2  | Code with explicit data path components             | 161 |

|   |     | 7.2.3  | Code with implicit data path components             | 164 |

|   |     | 7.2.4  | Comparison                                          | 166 |

|   | 7.3 | Desigr | n examples                                          | 168 |

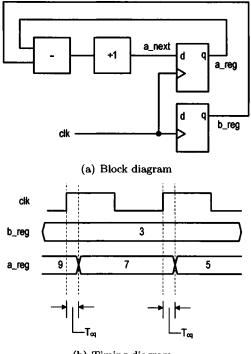

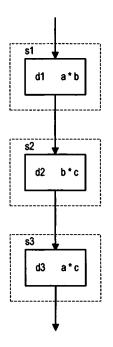

|   |     | 7.3.1  | Fibonacci number circuit                            | 168 |

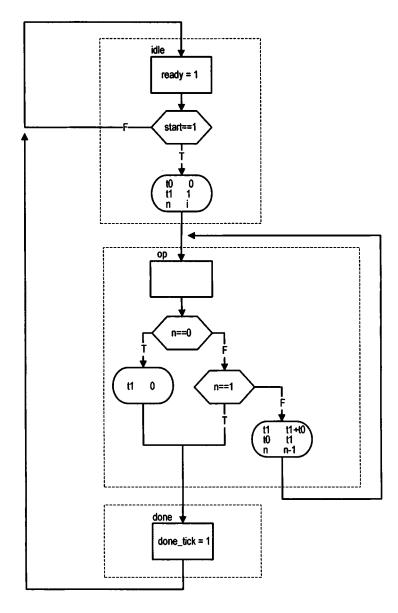

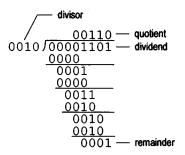

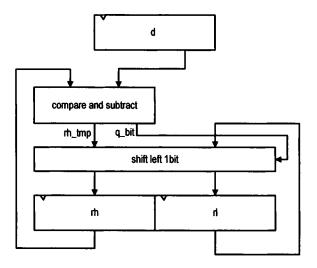

|   |     | 7.3.2  | Division circuit                                    | 171 |

|   |     | 7.3.3  | Binary-to-BCD conversion circuit                    | 175 |

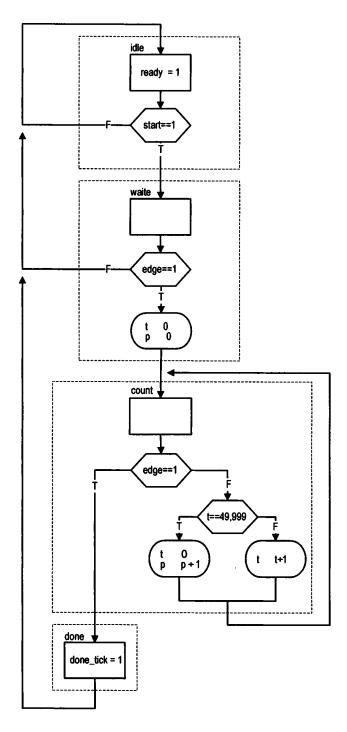

|   |     | 7.3.4  | Period counter                                      | 178 |

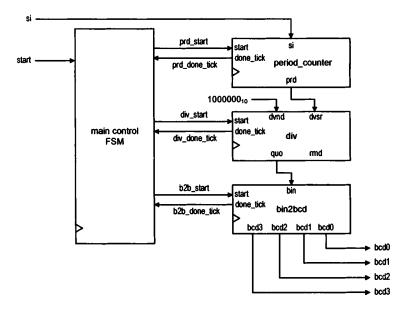

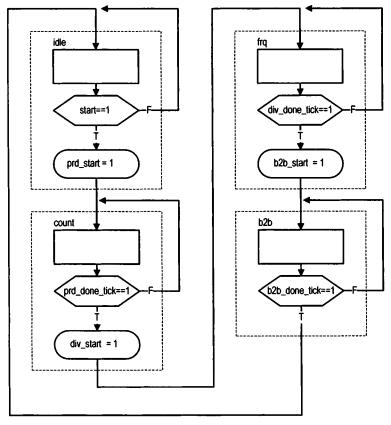

|   |     | 7.3.5  | Accurate low-frequency counter                      | 181 |

|   | 7.4 | Biblio | graphic notes                                       | 184 |

|   | 7.5 | Sugge  | sted experiments                                    | 184 |

|   |     | 7.5.1  | Alternative debouncing circuit                      | 184 |

|   |     | 7.5.2  | BCD-to-binary conversion circuit                    | 184 |

|   |     | 7.5.3  | Fibonacci circuit with BCD I/O: design approach $1$ | 185 |

|   |     | 7.5.4  | Fibonacci circuit with BCD I/O: design approach $2$ | 185 |

|   |     | 7.5.5  | Auto-scaled low-frequency counter                   | 186 |

|   |     | 7.5.6  | Reaction timer                                      | 186 |

|   |     | 7.5.7  | Babbage difference engine emulation circuit         | 187 |

| 8 | Sele | cted To | pics of Verilog                                          | 189 |

|---|------|---------|----------------------------------------------------------|-----|

|   | 8.1  | Blockin | ng versus nonblocking assignment                         | 189 |

|   |      | 8.1.1   | Overview                                                 | 190 |

|   |      | 8.1.2   | Combinational circuit                                    | 191 |

|   |      | 8.1.3   | Memory element                                           | 193 |

|   |      | 8.1.4   | Sequential circuit with mixed blocking and nonblocking   |     |

|   |      |         | assignments                                              | 194 |

|   | 8.2  | Alterna | ative coding style for sequential circuit                | 196 |

|   |      | 8.2.1   | Binary counter                                           | 196 |

|   |      | 8.2.2   | FSM                                                      | 198 |

|   |      | 8.2.3   | FSMD                                                     | 199 |

|   |      | 8.2.4   | Summary                                                  | 201 |

|   | 8.3  | Use of  | the signed data type                                     | 201 |

|   |      | 8.3.1   | Overview                                                 | 201 |

|   |      | 8.3.2   | Signed number in Verilog-1995                            | 203 |

|   |      | 8.3.3   | Signed number in Verilog-2001                            | 203 |

|   | 8.4  | Use of  | function in synthesis                                    | 204 |

|   |      | 8.4.1   | Overview                                                 | 204 |

|   |      | 8.4.2   | Examples                                                 | 205 |

|   | 8.5  | Additic | onal constructs for testbench development                | 207 |

|   |      | 8.5.1   | Always block and initial block                           | 207 |

|   |      | 8.5.2   | Procedural statements                                    | 207 |

|   |      | 8.5.3   | Timing control                                           | 209 |

|   |      | 8.5.4   | Delay control                                            | 209 |

|   |      | 8.5.5   | Event control                                            | 210 |

|   |      | 8.5.6   | Wait statement                                           | 211 |

|   |      | 8.5.7   | Timescale directive                                      | 211 |

|   |      | 8.5.8   | System functions and tasks                               | 212 |

|   |      | 8.5.9   | User-defined functions and tasks                         | 216 |

|   |      | 8.5.10  | Example of a comprehensive testbench                     | 217 |

|   | 8.6  | 0       | raphic notes                                             | 223 |

|   | 8.7  |         | ted experiments                                          | 223 |

|   |      | 8.7.1   | Shift register with blocking and nonblocking assignments | 223 |

|   |      | 8.7.2   | Alternative coding style for BCD counter                 | 224 |

|   |      | 8.7.3   | Alternative coding style for FIFO buffer                 | 224 |

|   |      | 8.7.4   | Alternative coding style for Fibonacci circuit           | 224 |

|   |      | 8.7.5   | Dual-mode comparator                                     | 224 |

|   |      | 8.7.6   | Enhanced binary counter monitor                          | 224 |

|   |      | 8.7.7   | Testbench for FIFO buffer                                | 225 |

# PART II BASIC NIOS II SOFTWARE DEVELOPMENT

| 9  | Nios | II Proce | essor Overview                                              | 229        |

|----|------|----------|-------------------------------------------------------------|------------|

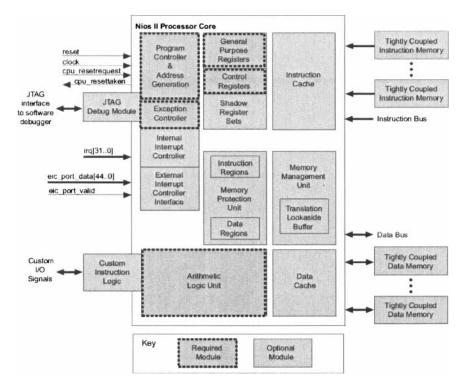

|    | 9.1  | Introdu  | ction                                                       | 229        |

|    | 9.2  | Register | r file and ALU                                              | 231        |

|    |      | 9.2.1    | Register file                                               | 231        |

|    |      | 9.2.2    | ALU                                                         | 231        |

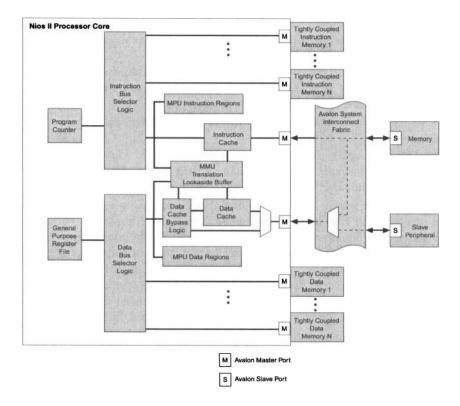

|    | 9.3  | Memory   | y and I/O organization                                      | 232        |

|    |      | 9.3.1    | Nios II memory interface                                    | 232        |

|    |      | 9.3.2    | Overview of memory hierarchy                                | 232        |

|    |      | 9.3.3    | Virtual memory                                              | 232        |

|    |      | 9.3.4    | Memory protection                                           | 233        |

|    |      | 9.3.5    | Cache memory                                                | 233        |

|    |      | 9.3.6    | Tightly coupled memory                                      | <b>234</b> |

|    |      | 9.3.7    | I/O organization                                            | <b>234</b> |

|    |      | 9.3.8    | Interconnect structure                                      | 235        |

|    | 9.4  | Excepti  | on and interrupt handler                                    | 235        |

|    | 9.5  | JTAG o   | lebug module                                                | 235        |

|    | 9.6  | Bibliog  | raphic notes                                                | <b>235</b> |

|    | 9.7  | Suggest  | ed projects                                                 | 236        |

|    |      | 9.7.1    | Comparison of Nios II and MIPS                              | 236        |

| 10 | Nios | II Syste | m Derivation and Low-Level Access                           | 237        |

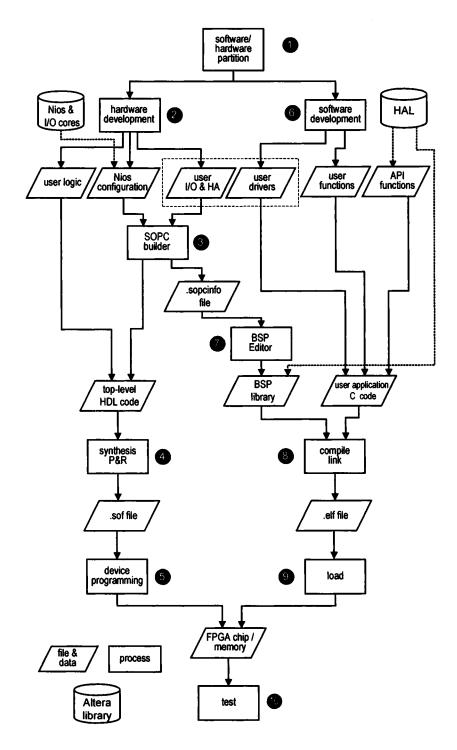

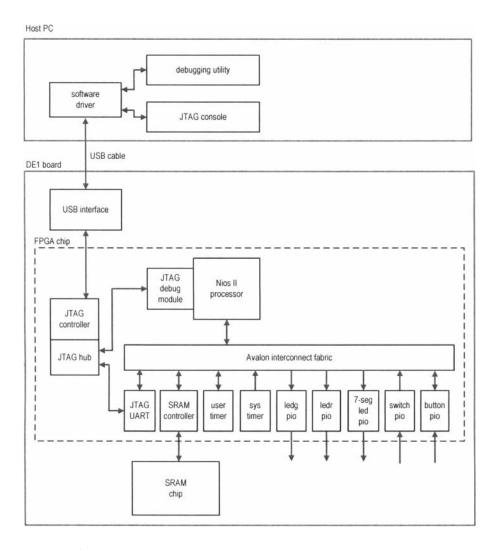

|    | 10.1 | Develop  | oment flow revisited                                        | 237        |

|    |      | 10.1.1   | Hardware development                                        | 237        |

|    |      | 10.1.2   | Software development                                        | 239        |

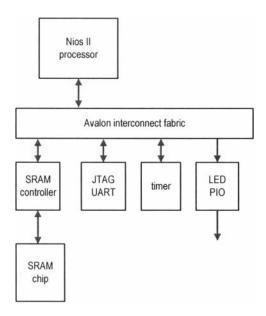

|    |      | 10.1.3   | Flashing-LED system                                         | 239        |

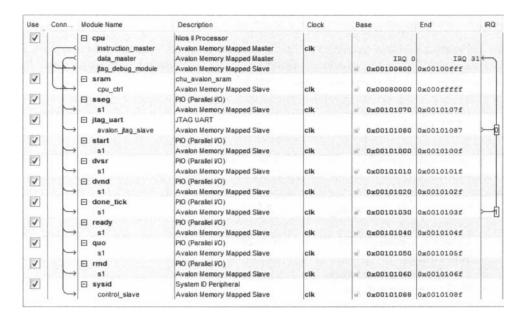

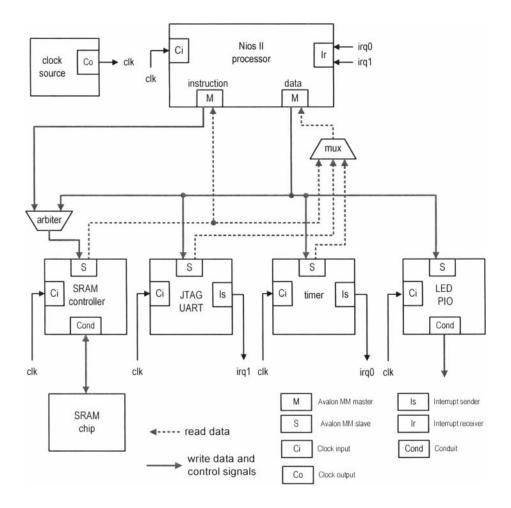

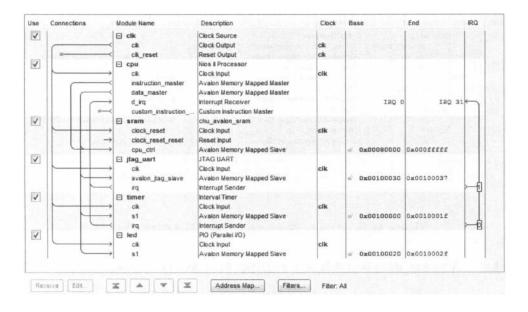

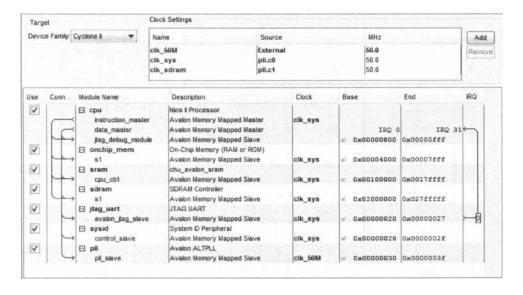

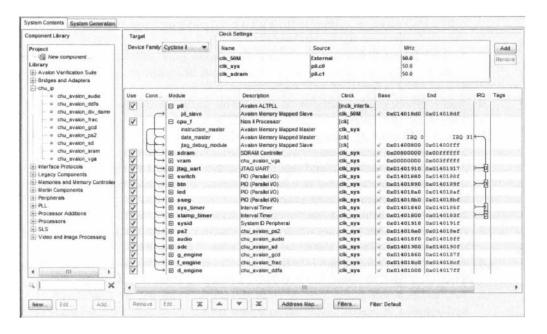

|    | 10.2 | Nios II  | hardware generation tutorial                                | 240        |

|    |      | 10.2.1   | Create a hardware project in Quartus II                     | 240        |

|    |      | 10.2.2   | Create a Nios II system and generate HDL codes              | 240        |

|    |      | 10.2.3   | Create a top-level HDL file that instantiates the Nios II   |            |

|    |      |          | system                                                      | 246        |

|    |      | 10.2.4   | Compiling and programming                                   | 247        |

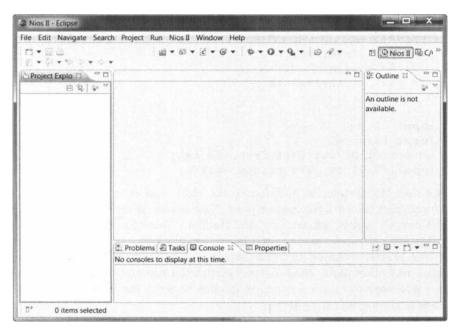

|    | 10.3 | Nios II  | SBT GUI tutorial                                            | 248        |

|    |      | 10.3.1   | Create BSP library                                          | 248        |

|    |      | 10.3.2   | Configure the BSP using BSP Editor                          | 249        |

|    |      | 10.3.3   | Create user application directory and add application files | 250        |

|    |      | 10.3.4   | Build and run software                                      | 251        |

|    |      | 10.3.5   | Check code size                                             | 252        |

|    | 10.4 | System   | id core for hardware-software consistency                   | 252        |

|    | 10.5 | Direct l | low-level I/O access                                        | 254        |

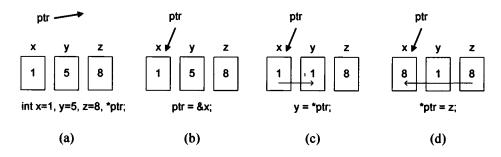

|    |      | 10.5.1   | Review of C pointer                                         | 254        |

|    |      | 10.5.2   | C pointer for I/O register                                  | 255        |

|    | 10.6  | Robust  | low-level I/O access                                  | 256 |

|----|-------|---------|-------------------------------------------------------|-----|

|    |       | 10.6.1  | system.h                                              | 256 |

|    |       | 10.6.2  | alt_types.h                                           | 257 |

|    |       | 10.6.3  | io.h                                                  | 257 |

|    | 10.7  | Some C  | techniques for low-level I/O operations               | 258 |

|    |       | 10.7.1  | Bit manipulation                                      | 258 |

|    |       | 10.7.2  | Packing and unpacking                                 | 258 |

|    | 10.8  | Softwar | e development                                         | 259 |

|    |       | 10.8.1  | Basic embedded program architecture                   | 259 |

|    |       | 10.8.2  | Main program and task routines                        | 260 |

|    | 10.9  | Bibliog | raphic notes                                          | 261 |

|    | 10.10 | Suggest | ed experiments                                        | 261 |

|    |       | 10.10.1 | Chasing LED circuit                                   | 261 |

|    |       | 10.10.2 | Collision LED circuit                                 | 262 |

|    |       | 10.10.3 | Pulse width modulation circuit                        | 262 |

|    |       | 10.10.4 | Rotating square circuit                               | 262 |

|    |       | 10.10.5 | Heartbeat circuit                                     | 262 |

|    | 10.11 | Comple  | te program listing                                    | 263 |

| 11 | Pred  | esigned | Nios II I/O Peripherals                               | 265 |

|    | 11.1  | Overvie | 2WS                                                   | 265 |

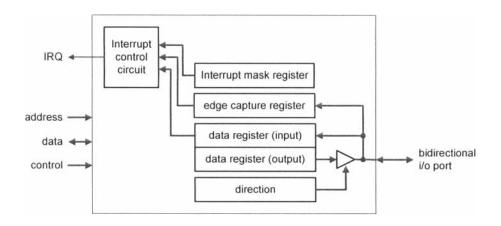

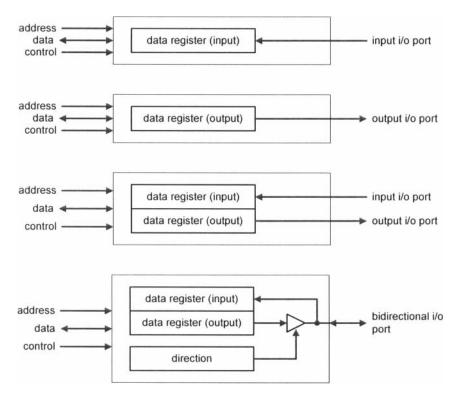

|    | 11.2  | PIO con | re                                                    | 266 |

|    |       | 11.2.1  | Configuration                                         | 266 |

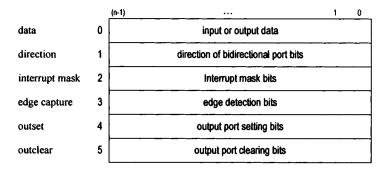

|    |       |         | Register map                                          | 269 |

|    |       |         | Visible register                                      | 270 |

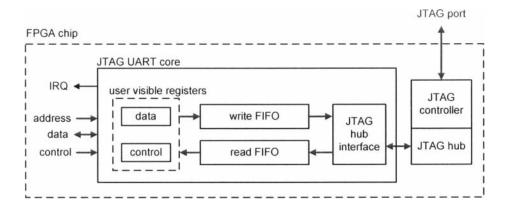

|    | 11.3  | JTAG U  | UART core                                             | 270 |

|    |       | 11.3.1  | Configuration                                         | 270 |

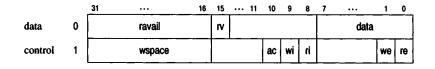

|    |       | 11.3.2  | Register map                                          | 271 |

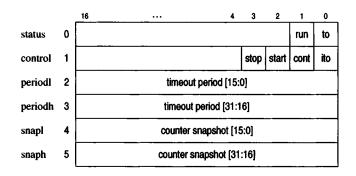

|    | 11.4  | Interna | l timer core                                          | 272 |

|    |       | 11.4.1  | Configuration                                         | 272 |

|    |       | 11.4.2  | Register map                                          | 273 |

|    | 11.5  | Enhanc  | ed flashing-LED Nios II system                        | 274 |

|    |       | 11.5.1  | SOPC design                                           | 274 |

|    |       | 11.5.2  | Top-level HDL file                                    | 278 |

|    | 11.6  | Softwar | e development of enhanced flashing-LED system         | 279 |

|    |       | 11.6.1  | Introduction to device driver                         | 280 |

|    |       | 11.6.2  | Program structure of the enhanced flashing-LED system | 280 |

|    |       | 11.6.3  | Main program                                          | 281 |

|    |       | 11.6.4  | Function naming convention                            | 281 |

|    | 11.7  | Device  | driver routines                                       | 282 |

|    |       | 11.7.1  | Driver for PIO peripherals                            | 282 |

|    |       | 11.7.2  | JTAG UART                                             | 284 |

|    |       | 11.7.3                                                                                                                      | Timer                                                                                                                                                                                                                                                                                                                                                               | 285                                                                                            |

|----|-------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|    | 11.8  | Task ro                                                                                                                     | utines                                                                                                                                                                                                                                                                                                                                                              | 286                                                                                            |

|    |       | 11.8.1                                                                                                                      | The flashsys_init_v1() function                                                                                                                                                                                                                                                                                                                                     | 287                                                                                            |

|    |       | 11.8.2                                                                                                                      | The sw_get_command_v1() function                                                                                                                                                                                                                                                                                                                                    | 287                                                                                            |

|    |       | 11.8.3                                                                                                                      | The jtaguart_disp_msg_v1() function                                                                                                                                                                                                                                                                                                                                 | 287                                                                                            |

|    |       | 11.8.4                                                                                                                      | The sseg_disp_msg_v1() function                                                                                                                                                                                                                                                                                                                                     | 288                                                                                            |

|    |       | 11.8.5                                                                                                                      | The led_flash_v1() function                                                                                                                                                                                                                                                                                                                                         | 289                                                                                            |

|    | 11.9  | Softwar                                                                                                                     | e construction and testing                                                                                                                                                                                                                                                                                                                                          | 289                                                                                            |

|    | 11.10 | ) Bibliogr                                                                                                                  | raphic notes                                                                                                                                                                                                                                                                                                                                                        | 290                                                                                            |

|    | 11.11 | . Suggest                                                                                                                   | ed experiments                                                                                                                                                                                                                                                                                                                                                      | 290                                                                                            |

|    |       | 11.11.1                                                                                                                     | "Uptime" feature in flashing-LED system                                                                                                                                                                                                                                                                                                                             | 290                                                                                            |

|    |       | 11.11.2                                                                                                                     | Counting with different timer mode                                                                                                                                                                                                                                                                                                                                  | 290                                                                                            |

|    |       | 11.11.3                                                                                                                     | JTAG UART input                                                                                                                                                                                                                                                                                                                                                     | 290                                                                                            |

|    |       | 11.11.4                                                                                                                     | Enhanced collision LED circuit                                                                                                                                                                                                                                                                                                                                      | 290                                                                                            |

|    |       | 11.11.5                                                                                                                     | Rotating LED banner circuit                                                                                                                                                                                                                                                                                                                                         | 291                                                                                            |

|    |       | 11.11.6                                                                                                                     | Enhanced stopwatch                                                                                                                                                                                                                                                                                                                                                  | 291                                                                                            |

|    |       | 11.11.7                                                                                                                     | Parking lot occupancy counter                                                                                                                                                                                                                                                                                                                                       | 291                                                                                            |

|    |       | 11.11.8                                                                                                                     | Reaction timer with pushbutton switch control                                                                                                                                                                                                                                                                                                                       | 291                                                                                            |

|    |       | 11.11.9                                                                                                                     | Reaction timer with keyboard control                                                                                                                                                                                                                                                                                                                                | 291                                                                                            |

|    |       | 11.11.10                                                                                                                    | Communication with serial port                                                                                                                                                                                                                                                                                                                                      | 292                                                                                            |

|    | 11.12 | 2 Comple                                                                                                                    | te program listing                                                                                                                                                                                                                                                                                                                                                  | 293                                                                                            |

|    |       |                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                |

| 12 | Pred  | esigned                                                                                                                     | Nios II I/O Drivers and HAL API                                                                                                                                                                                                                                                                                                                                     | 303                                                                                            |

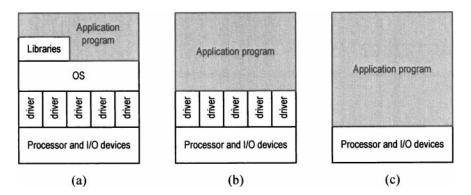

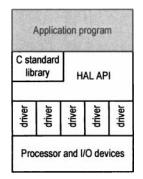

|    | 12.1  | Overvie                                                                                                                     | w of HAL                                                                                                                                                                                                                                                                                                                                                            | 303                                                                                            |

|    |       | 12.1.1                                                                                                                      | Desktop-like and barebone embedded systems                                                                                                                                                                                                                                                                                                                          | 304                                                                                            |

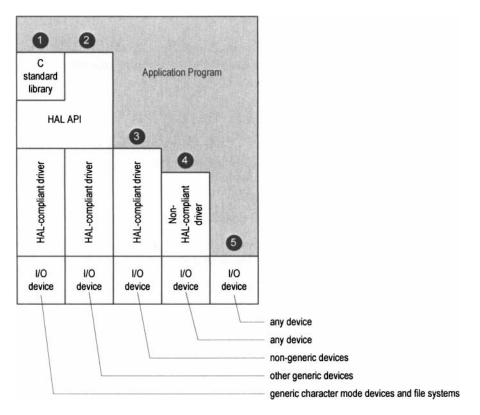

|    |       | 12.1.2                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                     | 305                                                                                            |

|    |       | 12.1.3                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                |

|    |       |                                                                                                                             | Device classes                                                                                                                                                                                                                                                                                                                                                      | 306                                                                                            |

|    |       | 12.1.4                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                     | 306<br>307                                                                                     |

|    |       |                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                |

|    |       | 12.1.4                                                                                                                      | HAL-compliant device drivers                                                                                                                                                                                                                                                                                                                                        | 307                                                                                            |

|    | 12.2  | 12.1.4<br>12.1.5                                                                                                            | HAL-compliant device drivers<br>The <b>_regs.h</b> file                                                                                                                                                                                                                                                                                                             | 307<br>307                                                                                     |

|    | 12.2  | $12.1.4 \\ 12.1.5 \\ 12.1.6$                                                                                                | HAL-compliant device drivers<br>The <b>_regs.h</b> file                                                                                                                                                                                                                                                                                                             | 307<br>307<br>308                                                                              |

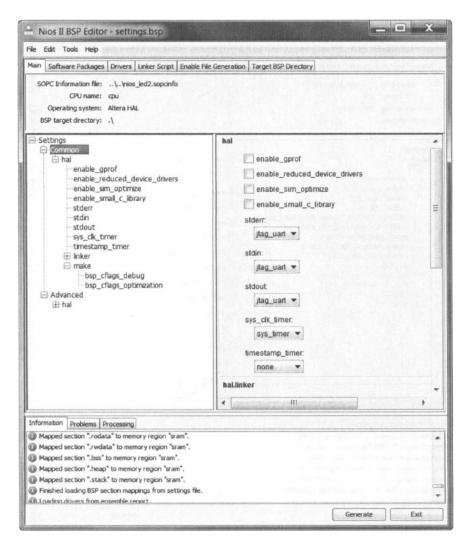

|    | 12.2  | 12.1.4<br>12.1.5<br>12.1.6<br>BSP                                                                                           | HAL-compliant device drivers<br>The _regs.h file<br>HAL-based initialization sequence                                                                                                                                                                                                                                                                               | 307<br>307<br>308<br>309                                                                       |

|    | 12.2  | 12.1.4<br>12.1.5<br>12.1.6<br>BSP<br>12.2.1                                                                                 | HAL-compliant device drivers<br>The _regs.h file<br>HAL-based initialization sequence<br>Overview                                                                                                                                                                                                                                                                   | 307<br>307<br>308<br>309<br>309                                                                |

|    |       | 12.1.4<br>12.1.5<br>12.1.6<br>BSP<br>12.2.1<br>12.2.2<br>12.2.3                                                             | HAL-compliant device drivers<br>The _regs.h file<br>HAL-based initialization sequence<br>Overview<br>BSP file structure                                                                                                                                                                                                                                             | 307<br>307<br>308<br>309<br>309<br>309                                                         |

|    |       | 12.1.4<br>12.1.5<br>12.1.6<br>BSP<br>12.2.1<br>12.2.2<br>12.2.3                                                             | HAL-compliant device drivers<br>The _regs.h file<br>HAL-based initialization sequence<br>Overview<br>BSP file structure<br>BSP configuration                                                                                                                                                                                                                        | 307<br>307<br>308<br>309<br>309<br>309<br>309<br>309                                           |

|    |       | 12.1.4<br>12.1.5<br>12.1.6<br>BSP<br>12.2.1<br>12.2.2<br>12.2.3<br>HAL-ba                                                   | HAL-compliant device drivers<br>The _regs.h file<br>HAL-based initialization sequence<br>Overview<br>BSP file structure<br>BSP configuration<br>ased flashing-LED program                                                                                                                                                                                           | 307<br>307<br>308<br>309<br>309<br>309<br>309<br>309<br>313                                    |

|    |       | 12.1.4<br>12.1.5<br>12.1.6<br>BSP<br>12.2.1<br>12.2.2<br>12.2.3<br>HAL-ba<br>12.3.1                                         | HAL-compliant device drivers<br>The _regs.h file<br>HAL-based initialization sequence<br>Overview<br>BSP file structure<br>BSP configuration<br>ased flashing-LED program<br>Functions using generic I/O devices                                                                                                                                                    | 307<br>307<br>308<br>309<br>309<br>309<br>309<br>313<br>313                                    |

|    |       | 12.1.4<br>12.1.5<br>12.1.6<br>BSP<br>12.2.1<br>12.2.2<br>12.2.3<br>HAL-ba<br>12.3.1<br>12.3.2                               | HAL-compliant device drivers<br>The _regs.h file<br>HAL-based initialization sequence<br>Overview<br>BSP file structure<br>BSP configuration<br>ased flashing-LED program<br>Functions using generic I/O devices<br>Functions using non-generic I/O devices                                                                                                         | 307<br>307<br>308<br>309<br>309<br>309<br>309<br>313<br>313<br>313                             |

|    | 12.3  | 12.1.4<br>12.1.5<br>12.1.6<br>BSP<br>12.2.1<br>12.2.2<br>12.2.3<br>HAL-ba<br>12.3.1<br>12.3.2<br>12.3.3<br>12.3.4           | HAL-compliant device drivers<br>The _regs.h file<br>HAL-based initialization sequence<br>Overview<br>BSP file structure<br>BSP configuration<br>ased flashing-LED program<br>Functions using generic I/O devices<br>Functions using non-generic I/O devices<br>Initialization routine and main program                                                              | 307<br>307<br>308<br>309<br>309<br>309<br>309<br>313<br>313<br>313<br>315<br>316               |

|    | 12.3  | 12.1.4<br>12.1.5<br>12.1.6<br>BSP<br>12.2.1<br>12.2.2<br>12.2.3<br>HAL-ba<br>12.3.1<br>12.3.2<br>12.3.3<br>12.3.4           | HAL-compliant device drivers<br>The _regs.h file<br>HAL-based initialization sequence<br>Overview<br>BSP file structure<br>BSP configuration<br>ased flashing-LED program<br>Functions using generic I/O devices<br>Functions using non-generic I/O devices<br>Initialization routine and main program<br>Software construction and testing                         | 307<br>307<br>308<br>309<br>309<br>309<br>309<br>313<br>313<br>313<br>315<br>316<br>317        |

|    | 12.3  | 12.1.4<br>12.1.5<br>12.1.6<br>BSP<br>12.2.1<br>12.2.2<br>12.2.3<br>HAL-ba<br>12.3.1<br>12.3.2<br>12.3.3<br>12.3.4<br>Device | HAL-compliant device drivers<br>The _regs.h file<br>HAL-based initialization sequence<br>Overview<br>BSP file structure<br>BSP configuration<br>ased flashing-LED program<br>Functions using generic I/O devices<br>Functions using non-generic I/O devices<br>Initialization routine and main program<br>Software construction and testing<br>driver consideration | 307<br>307<br>308<br>309<br>309<br>309<br>309<br>313<br>313<br>313<br>315<br>316<br>317<br>318 |

|         | 12.4.3    | Device drivers in this book                    | 320 |

|---------|-----------|------------------------------------------------|-----|

| 12.5    | 5 Bibliog | graphic notes                                  | 321 |

| 12.6    | 5 Sugges  | ted experiments                                | 321 |

|         | 12.6.1    | "Uptime" feature in flashing-LED system        | 321 |

|         | 12.6.2    | Enhanced collision LED circuit                 | 322 |

|         | 12.6.3    | Parking lot occupancy counter                  | 322 |

|         | 12.6.4    | Reaction timer with keyboard control           | 322 |

|         | 12.6.5    | Digital alarm clock                            | 322 |

| 12.7    | 7 Comple  | ete program listing                            | 323 |

| 13 Inte | errupt an | d ISR                                          | 325 |

| 13.1    | Interru   | pt processing in the HAL framework             | 325 |

|         | 13.1.1    | Overview                                       | 326 |

|         | 13.1.2    | Interrupt controller of the Nios II processor  | 326 |

|         | 13.1.3    | Top-level exception handler                    | 327 |

|         | 13.1.4    | Interrupt service routines                     | 328 |

| 13.2    | 2 Interru | pt-based flashing-LED program                  | 328 |

|         | 13.2.1    | Interrupt of timer core                        | 329 |

|         | 13.2.2    | Driver of timer core                           | 329 |

|         | 13.2.3    | ISR version 1                                  | 330 |

|         | 13.2.4    | ISR version 2                                  | 332 |

| 13.     | 3 Interru | upt and scheduling                             | 333 |

|         | 13.3.1    | Scheduling                                     | 333 |

|         | 13.3.2    | Performance                                    | 335 |

| 13.4    | 4 Bibliog | graphic notes                                  | 336 |

| 13.     | 5 Sugges  | ted experiments                                | 336 |

|         | 13.5.1    | Flashing-LED system with pushbutton switch ISR | 336 |

|         | 13.5.2    | ISR-driven flashing-LED system                 | 336 |

|         |           | "Uptime" feature in flashing-LED system        | 337 |

|         |           | Reaction timer with keyboard control           | 337 |

|         | 13.5.5    | Digital alarm clock                            | 337 |

| 13.0    | -         | ete program listing                            | 338 |

|         |           | III CUSTOM I/O PERIPHERAL DEVELOPMENT          |     |

|         | -         | Peripheral with PIO Cores                      | 345 |

|         | I Introdu |                                                | 345 |

| 14.     |           | ation of division circuit to a Nios II system  | 346 |

|         | 14.2.1    | PIO modules                                    | 346 |

|         | 14.2.2    | Integration                                    | 347 |

|         | 3 Testing | -                                              | 347 |

| 14.4    | 4 Sugges  | sted experiments                               | 350 |

|         | 14.4.1   | Division core ISR                                  | 350 |

|---------|----------|----------------------------------------------------|-----|

|         | 14.4.2   | Division core with eight-bit data                  | 350 |

|         | 14.4.3   | Division core with 64-bit data                     | 350 |

|         | 14.4.4   | Fibonacci number circuit                           | 350 |

|         | 14.4.5   | Period counter                                     | 350 |

| 15 Aval | on Inter | rconnect and SOPC Component                        | 351 |

| 15.1    | Introdu  | iction                                             | 351 |

| 15.2    | Avalon   | MM interface                                       | 355 |

|         | 15.2.1   | Avalon MM slave interface signals                  | 355 |

|         | 15.2.2   | Avalon MM slave interface properties               | 356 |

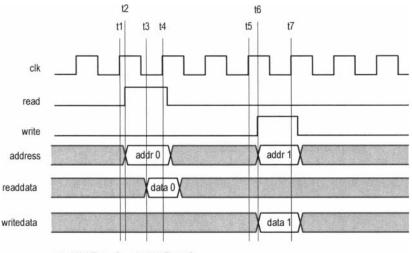

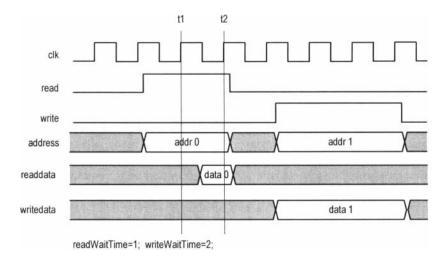

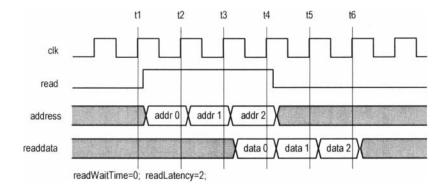

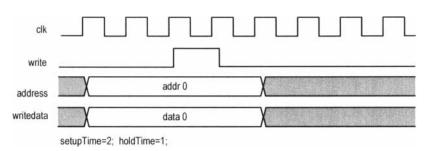

|         | 15.2.3   | Avalon MM slave timing                             | 356 |

| 15.3    | System   | interconnect fabric for Avalon interface           | 359 |

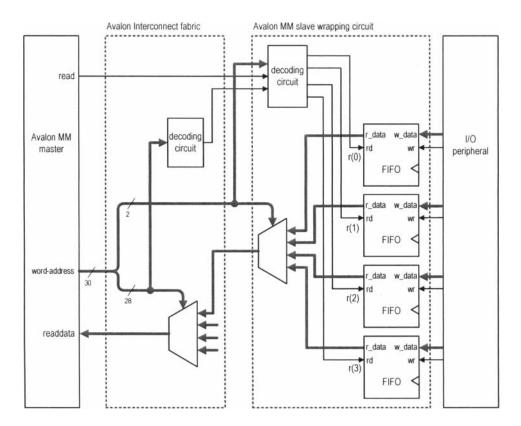

| 15.4    | SOPC     | I/O component wrapping circuit                     | 361 |

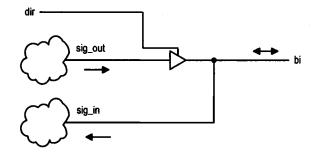

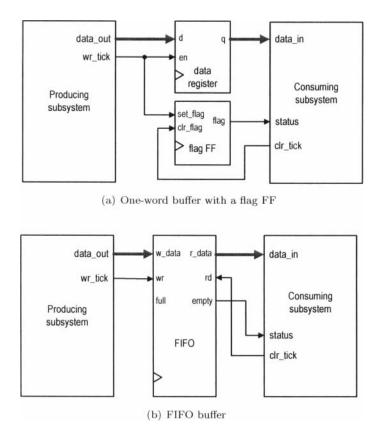

|         | 15.4.1   | Interface I/O buffer                               | 361 |

|         | 15.4.2   | Memory alignment                                   | 364 |

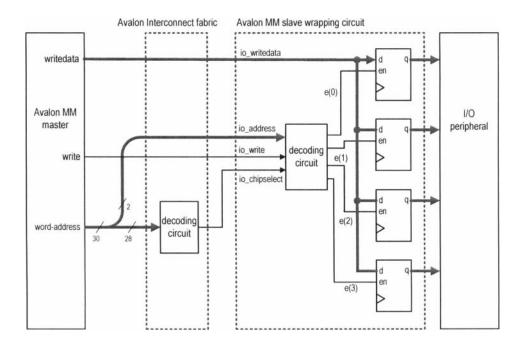

|         | 15.4.3   | Output decoding from an Avalon MM master           | 364 |

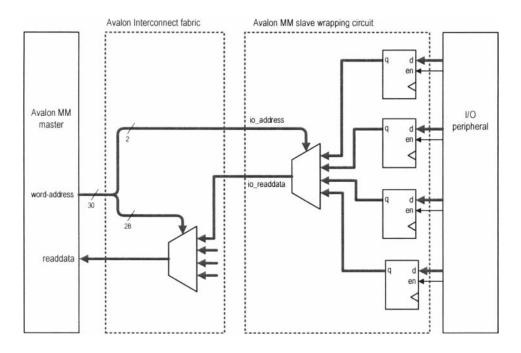

|         | 15.4.4   | Input multiplexing to an Avalon MM master          | 366 |

|         | 15.4.5   | Practical consideration                            | 367 |

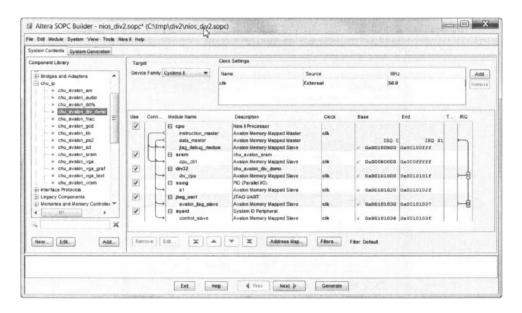

| 15.5    | SOPC     | component construction tutorial                    | 368 |

|         | 15.5.1   | Avalon interfaces                                  | 368 |

|         | 15.5.2   | Register map                                       | 369 |

|         | 15.5.3   | Wrapped division circuit                           | 370 |

|         | 15.5.4   | SOPC component creation                            | 372 |

|         | 15.5.5   | SOPC component instantiation                       | 379 |

| 15.6    | Testing  | 5                                                  | 381 |

| 15.7    | Bibliog  | graphic notes                                      | 383 |

| 15.8    | Sugges   | ted experiments                                    | 383 |

|         | 15.8.1   | Division core ISR                                  | 383 |

|         | 15.8.2   | Alternative buffering scheme for the division core | 383 |

|         | 15.8.3   | Division core with eight-bit data                  | 384 |

|         | 15.8.4   | Division core with 64-bit data                     | 384 |

|         | 15.8.5   | Fibonacci number circuit                           | 384 |

|         | 15.8.6   | Period counter                                     | 384 |

| 16 SRA  | M and    | SDRAM Controllers                                  | 385 |

| 16.1    | Memor    | ry resources of DE1 board                          | 385 |

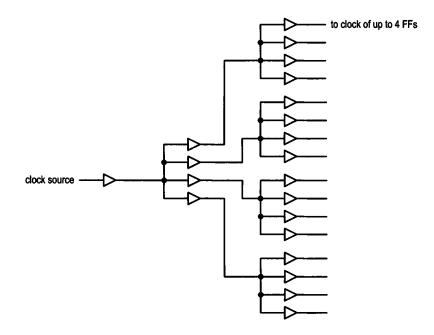

| 16.2    | Brief o  | verview of timing and clock management             | 386 |

|         | 16.2.1   | Clock distribution network                         | 386 |

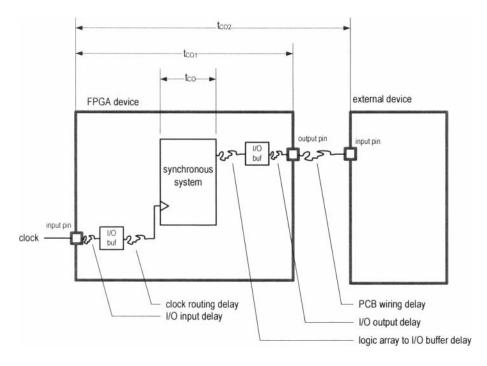

|         | 16.2.2   | Timing consideration of off-chip access            | 387 |

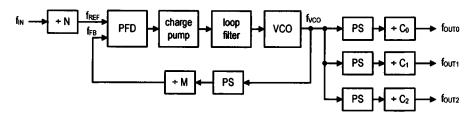

|         | 16.2.3   | PLL                                                | 388 |

|         |          |                                                    |     |

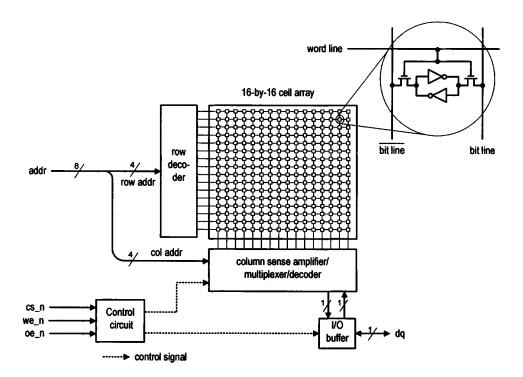

|    | 16.3  | Overvie   | ew of SRAM                                        | 389         |

|----|-------|-----------|---------------------------------------------------|-------------|

|    |       | 16.3.1    | SRAM cell                                         | 389         |

|    |       | 16.3.2    | Basic organization                                | 390         |

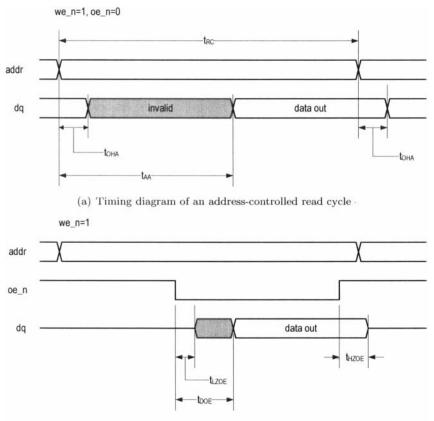

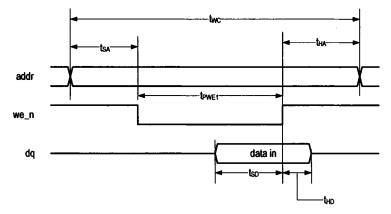

|    |       | 16.3.3    | Timing                                            | 391         |

|    |       | 16.3.4    | IS61LV25616AL SRAM device                         | 393         |

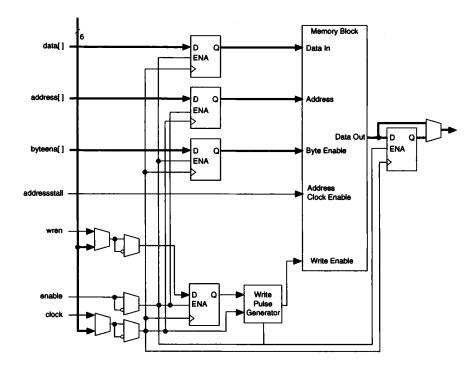

|    | 16.4  | SRAM      | controller IP core                                | 394         |

|    |       | 16.4.1    | Avalon interfaces                                 | 394         |

|    |       | 16.4.2    | Controller circuit                                | 396         |

|    |       | 16.4.3    | SOPC component creation                           | 397         |

|    | 16.5  | Overvie   | ew of DRAM                                        | <b>3</b> 98 |

|    |       | 16.5.1    | DRAM cell                                         | 398         |

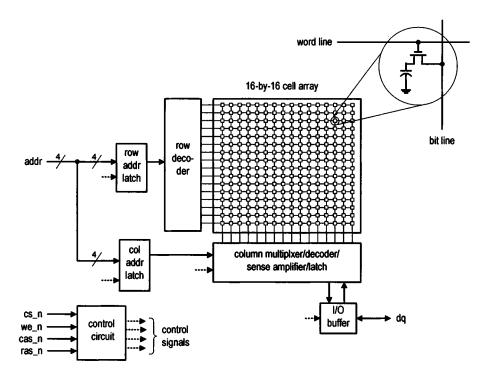

|    |       | 16.5.2    | Basic DRAM organization                           | 400         |

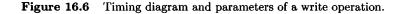

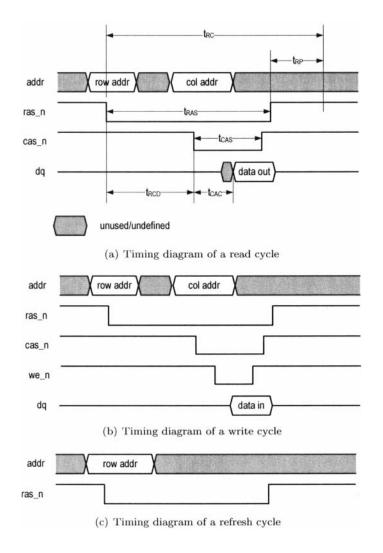

|    |       | 16.5.3    | DRAM timing                                       | 401         |

|    | 16.6  | Overvie   | ew of SDRAM                                       | 403         |

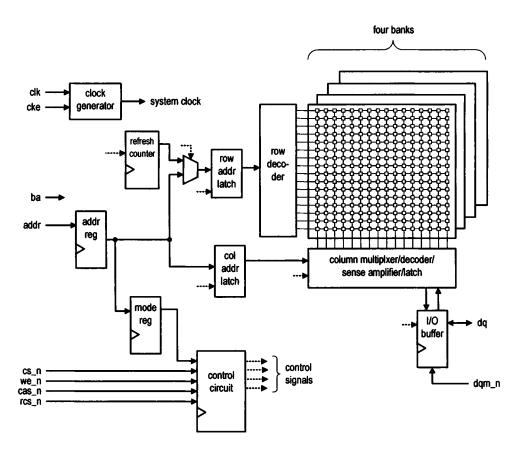

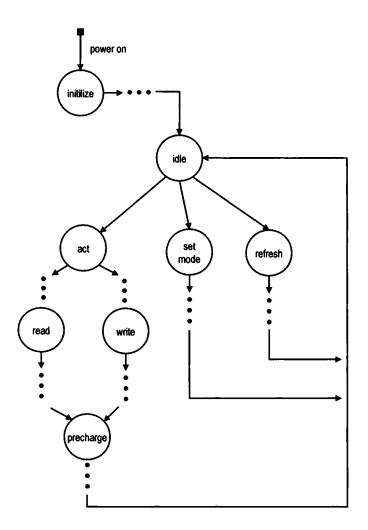

|    |       | 16.6.1    | Basic SDRAM organization                          | 403         |

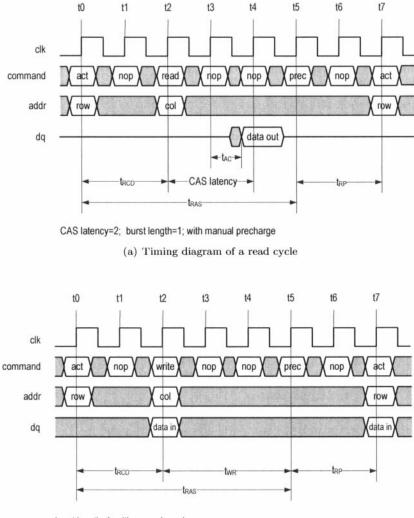

|    |       | 16.6.2    | SDRAM timing                                      | 404         |

|    |       | 16.6.3    | ICSI IS42S16400 SDRAM device                      | 406         |

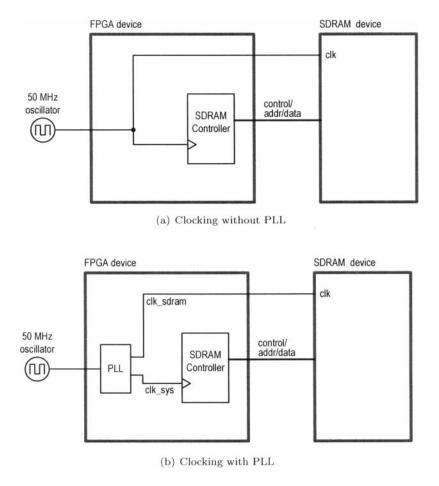

|    | 16.7  | SDRAM     | A controller and PLL                              | 406         |

|    |       | 16.7.1    | Basic SDRAM controller                            | 406         |

|    |       | 16.7.2    | SDRAM controller IP core                          | 408         |

|    |       | 16.7.3    | SOPC PLL IP core                                  | 408         |

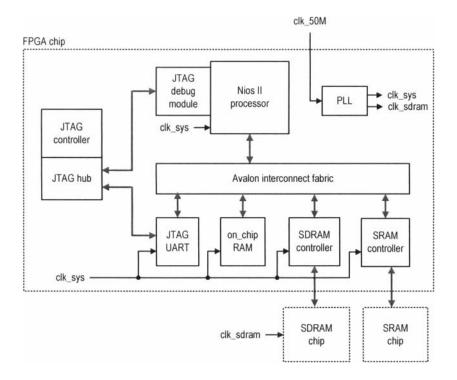

|    | 16.8  | Testing   | system                                            | 411         |

|    |       | 16.8.1    | Testing hardware configuration                    | 411         |

|    |       | 16.8.2    | Testing software                                  | 415         |

|    | 16.9  | Bibliog   | raphic notes                                      | 418         |

|    | 16.10 | ) Suggest | ed experiments                                    | 418         |

|    |       | 16.10.1   | SRAM controller without I/O register              | 418         |

|    |       | 16.10.2   | SRAM controller speed test                        | 418         |

|    |       | 16.10.3   | SRAM controller with Avalon MM tristate interface | 419         |

|    |       | 16.10.4   | SDRAM controller clock skew test                  | 419         |

|    |       | 16.10.5   | Memory performance comparison                     | 419         |

|    |       |           | Effect of cache memory                            | 419         |

|    |       | 16.10.7   | SDRAM controller from scratch                     | 419         |

|    | 16.11 | l Comple  | ete program listing                               | 420         |

| 17 | PS2   | Keyboa    | rd and Mouse                                      | 423         |

|    | 17.1  | Introdu   | iction                                            | 423         |

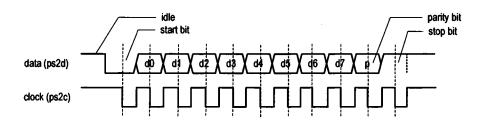

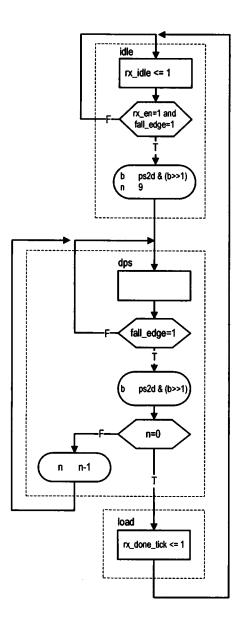

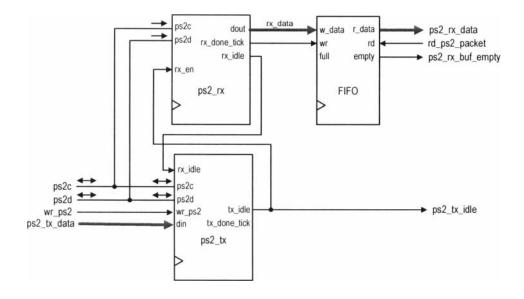

|    | 17.2  | PS2 rec   | ceiving subsystem                                 | 424         |

|    |       | 17.2.1    | PS2-device-to-host communication protocol         | 424         |

|    |       | 17.2.2    | Design and code                                   | 425         |

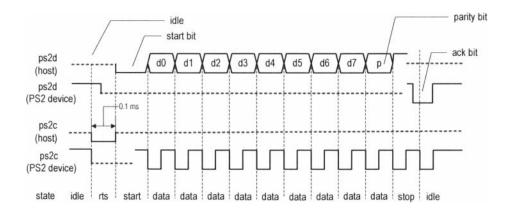

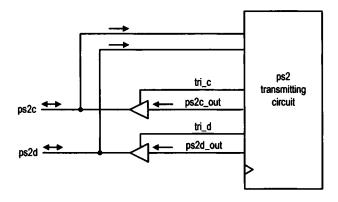

|    | 17.3  | PS2 tra   | ansmitting subsystem                              | 428         |

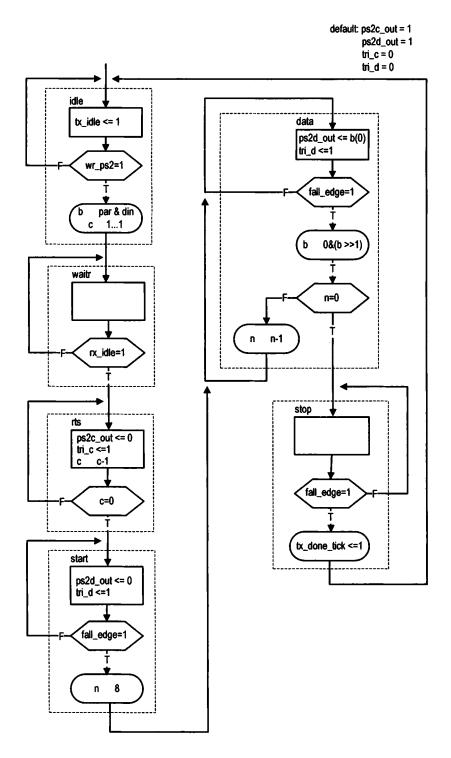

|    |       | 17.3.1    | Host-to-PS2-device communication protocol         | 428         |

|    |       | 17.3.2    | Design and code                             | 429 |

|----|-------|-----------|---------------------------------------------|-----|

|    | 17.4  | Comple    | ete PS2 system                              | 433 |

|    | 17.5  | PS2 con   | ntroller IP core development                | 435 |

|    |       | 17.5.1    | Avalon interfaces                           | 435 |

|    |       | 17.5.2    | Register map                                | 435 |

|    |       | 17.5.3    | Wrapped PS2 system                          | 436 |

|    |       | 17.5.4    | SOPC component creation                     | 437 |

|    | 17.6  | PS2 dri   | iver                                        | 438 |

|    |       | 17.6.1    | Register map                                | 438 |

|    |       | 17.6.2    | Write routines                              | 438 |

|    |       | 17.6.3    | Read routines                               | 439 |

|    | 17.7  | Keyboa    | ard driver                                  | 440 |

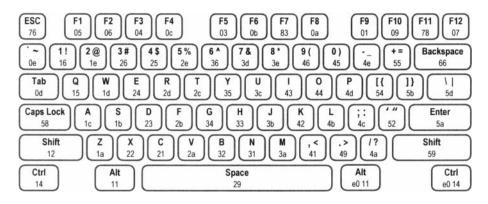

|    |       | 17.7.1    | Overview of the scan code                   | 440 |

|    |       | 17.7.2    | Interaction with host                       | 441 |

|    |       | 17.7.3    | Driver routines                             | 441 |

|    | 17.8  | Mouse     | driver                                      | 445 |

|    |       | 17.8.1    | Overview of PS2 mouse protocol              | 445 |

|    |       | 17.8.2    | Interaction with host                       | 446 |

|    |       | 17.8.3    | Driver routines                             | 447 |

|    | 17.9  | Test      |                                             | 449 |

|    | 17.10 | Use of    | book's custom IP cores                      | 451 |

|    |       | 17.10.1   | File organization                           | 451 |

|    |       | 17.10.2   | SOPC library integration                    | 452 |

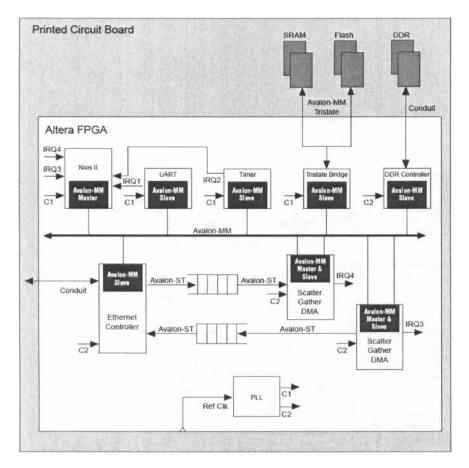

|    |       | 17.10.3   | Comprehensive Nios II testing system        | 452 |

|    | 17.11 | l Bibliog | raphic notes                                | 456 |

|    | 17.12 | 2 Suggest | ted experiments                             | 456 |

|    |       | 17.12.1   | PS2 receiving subsystem with watchdog timer | 456 |

|    |       | 17.12.2   | Software receiving FIFO                     | 458 |

|    |       | 17.12.3   | Software PS2 controller                     | 458 |

|    |       | 17.12.4   | Keyboard-controlled LED flashing circuit    | 458 |

|    |       | 17.12.5   | Enhanced keyboard driver routine I          | 458 |

|    |       | 17.12.6   | Enhanced keyboard driver routine II         | 458 |

|    |       | 17.12.7   | Remote-mode mouse driver                    | 459 |

|    |       |           | Scroll-wheel mouse driver                   | 459 |

|    | 17.13 | 3 Comple  | ete program listing                         | 460 |

| 18 | VGA   | Contro    | ller                                        | 475 |

|    | 18.1  | Introdu   | iction                                      | 475 |

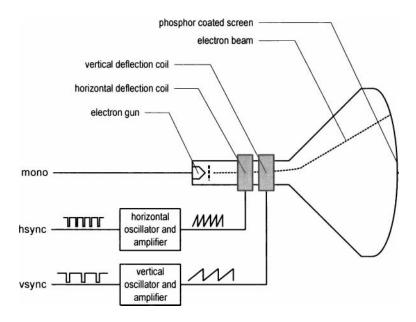

|    |       | 18.1.1    | Basic operation of a CRT                    | 475 |

|    |       | 18.1.2    | VGA port of the DE1 board                   | 477 |

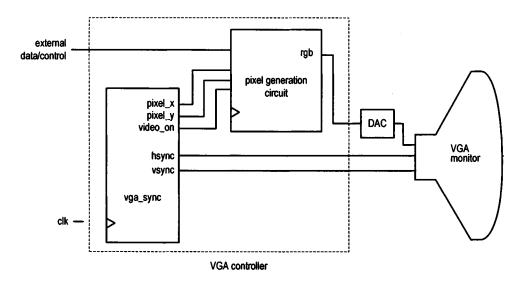

|    |       | 18.1.3    | Video controller                            | 478 |

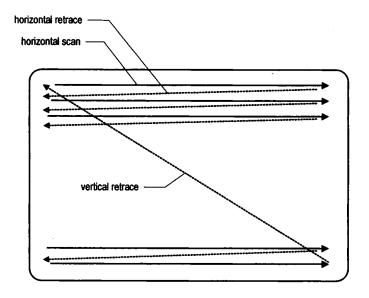

|    | 18.2  | VGA s     | ynchronization                              | 479 |

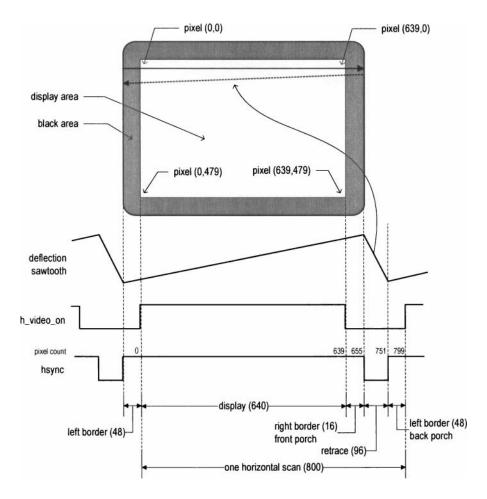

|      | 18.2.1  | Horizontal synchronization                        | 480 |

|------|---------|---------------------------------------------------|-----|

|      | 18.2.2  | Vertical synchronization                          | 481 |

|      | 18.2.3  | Timing calculation of VGA synchronization signals | 482 |

|      | 18.2.4  | HDL implementation                                | 482 |

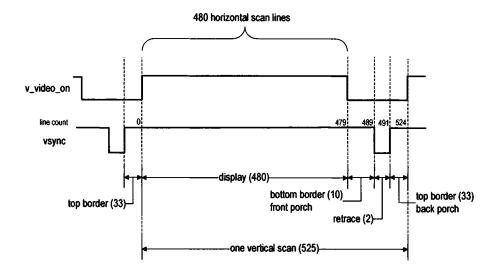

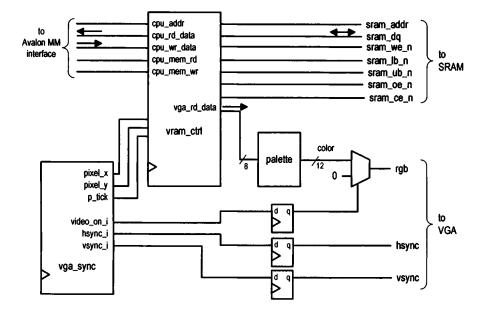

| 18.3 | SRAM-   | based video RAM controller                        | 484 |

|      | 18.3.1  | Overview of video memory                          | 484 |

|      | 18.3.2  | Memory consideration of DE1 board                 | 485 |

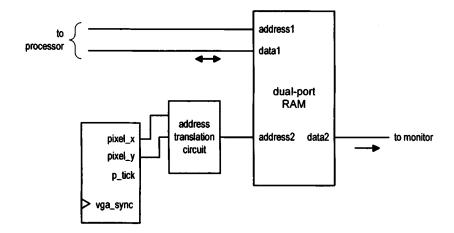

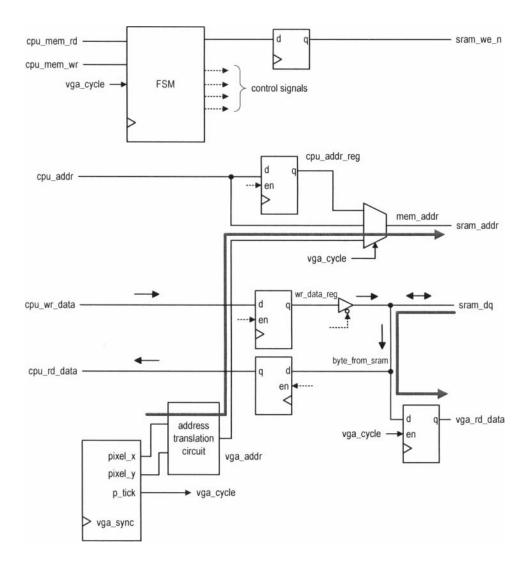

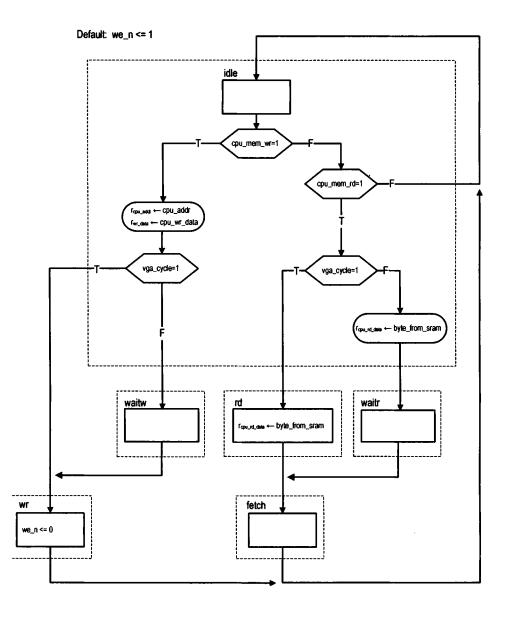

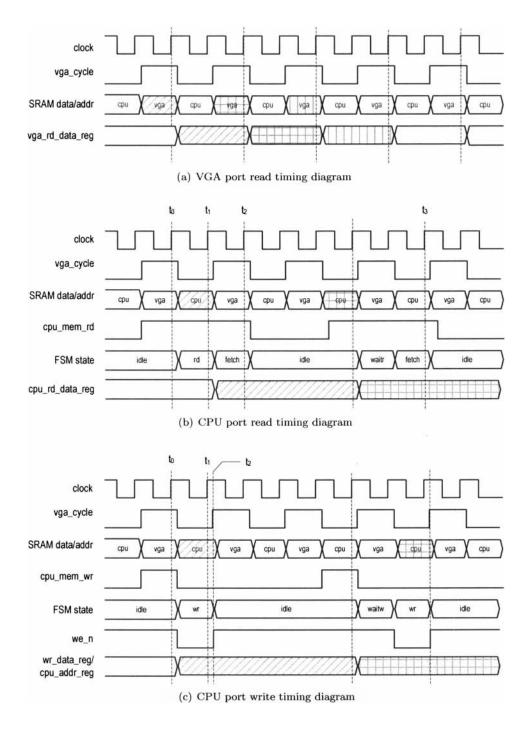

|      | 18.3.3  | Ad hoc SRAM controller                            | 486 |

|      | 18.3.4  | HDL code                                          | 491 |

| 18.4 | Palette | circuit                                           | 494 |

| 18.5 | Video c | ontroller IP core development                     | 495 |

|      | 18.5.1  | Complete video controller                         | 495 |

|      | 18.5.2  | Avalon interfaces                                 | 495 |

|      | 18.5.3  | Register map                                      | 496 |

|      | 18.5.4  | Wrapped video controller                          | 496 |

|      | 18.5.5  | SOPC component creation                           | 497 |

| 18.6 | Video d | lriver                                            | 498 |

|      | 18.6.1  | Video memory access routines                      | 498 |

|      | 18.6.2  | Geometrical model routine                         | 499 |

|      | 18.6.3  | Bitmap processing routines                        | 500 |

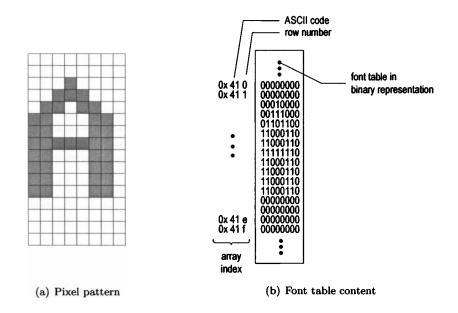

|      | 18.6.4  | Bit-mapped text routines                          | 503 |

| 18.7 | Mouse   | processing routines                               | 506 |

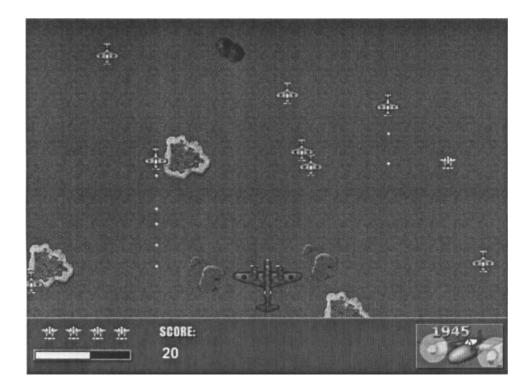

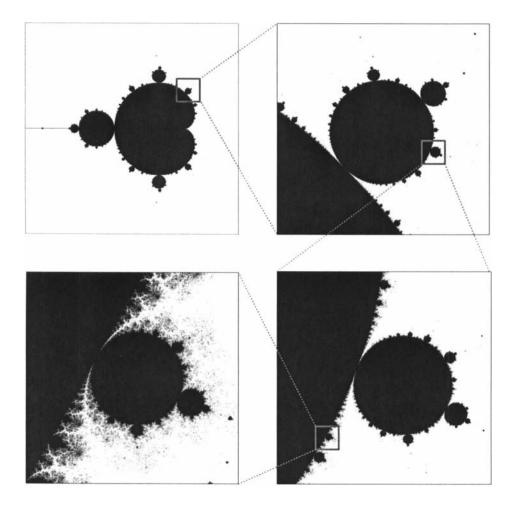

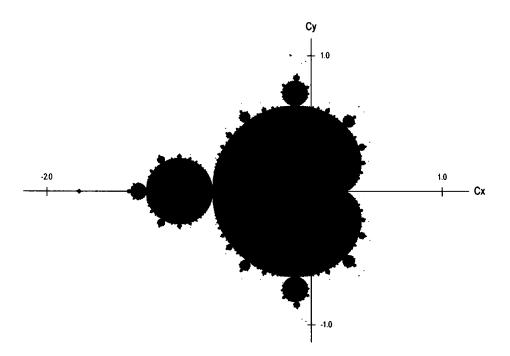

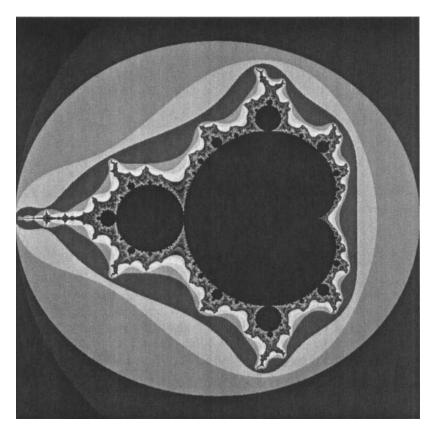

| 18.8 | Testing | program                                           | 507 |

|      | 18.8.1  | Chart plotting routine                            | 509 |

|      | 18.8.2  | General plotting functions                        | 510 |

|      | 18.8.3  | Strip swapping routine                            | 512 |

|      | 18.8.4  | Mouse demonstration routine                       | 512 |

|      | 18.8.5  | Bit-mapped text routine                           | 513 |

| 18.9 | Bitmap  | file processing                                   | 514 |

|      | 18.9.1  | BMP format overview                               | 514 |

|      | 18.9.2  | Generation of BMP file                            | 515 |

|      | 18.9.3  | Sprite-based design                               | 515 |

|      | 18.9.4  | BMP file access                                   | 516 |

|      | 18.9.5  | Host-based file system                            | 517 |

|      | 18.9.6  | Bitmap file retrieval routines                    | 519 |

|      | -       | raphic notes                                      | 522 |

| 18.1 |         | ed experiments                                    | 523 |

|      |         | PLL-based VGA controller                          | 523 |

|      |         | VGA controller with 16-bit memory configuration   | 523 |

|      |         | VGA controller with 3-bit color depth             | 523 |

|      |         | VGA controller with 1-bit color depth             | 523 |

|      | 18.11.5 | VGA controller with double buffering              | 523 |

|         | 18.11.6              | VGA controller with 320-by-240 resolution   | 523 |

|---------|----------------------|---------------------------------------------|-----|

|         | 18.11.7              | VGA controller with vertical mode operation | 524 |

|         | 18.11.8              | Geometrical model functions                 | 524 |

|         | 18.11.9              | Bitmap manipulation functions               | 524 |

|         | 18.11.10             | 0 Simulated "Etch A Sketch" toy             | 524 |

|         | 18.11.1              | 1 Palette lookup table circuit              | 524 |

|         | 18.11.12             | 2 Virtual LED flashing system panel         | 525 |

|         | 18.11.1              | 3 Virtual analog wall clock                 | 525 |

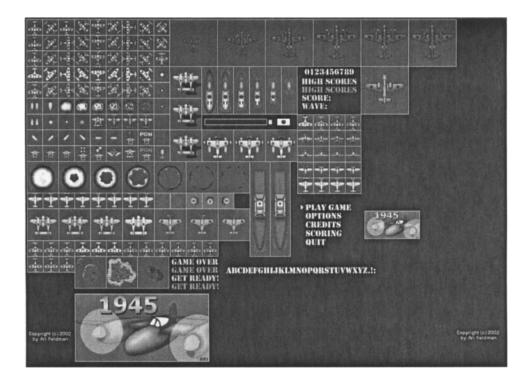

| 18.12   | 2 Suggest            | ted projects                                | 525 |

|         | 18.12.1              | Configurable VGA controller                 | 525 |

|         | 18.12.2              | VGA controller using system SDRAM           | 525 |

|         | 18.12.3              | Paint program                               | 525 |

|         | 18.12.4              | Video game                                  | 526 |

| 18.13   | 8 Comple             | ete program listing                         | 527 |

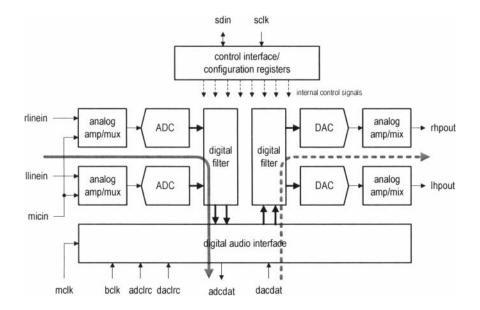

| 19 Audi | o Code               | c Controller                                | 555 |

| 19.1    | Introdu              | uction                                      | 555 |

|         | 19.1.1               | Overview of codec                           | 555 |

|         | 19.1.2               | Overview of WM8731 device                   | 556 |

|         | 19.1.3               | Registers of WM8731 device                  | 557 |

| 19.2    | I <sup>2</sup> C cor | ntroller                                    | 560 |

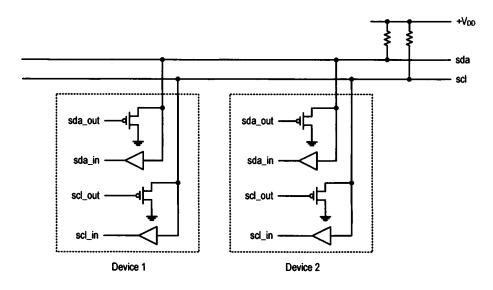

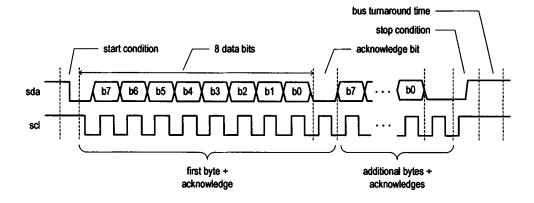

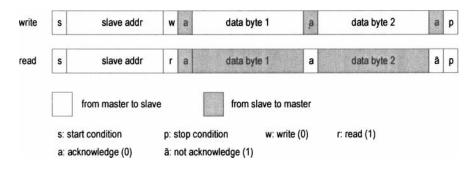

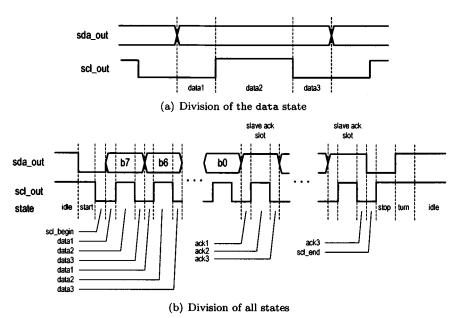

|         | 19.2.1               | Overview of I <sup>2</sup> C interface      | 560 |

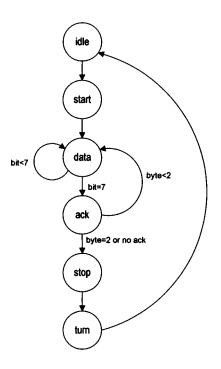

|         | 19.2.2               | HDL implementation                          | 562 |

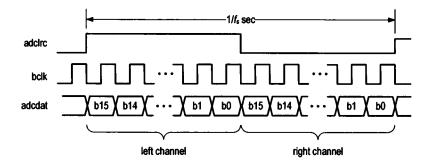

| 19.3    | Codec                | data access controller                      | 568 |

|         | 19.3.1               | Overview of digital audio interface         | 568 |

|         | 19.3.2               | HDL implementation                          | 569 |

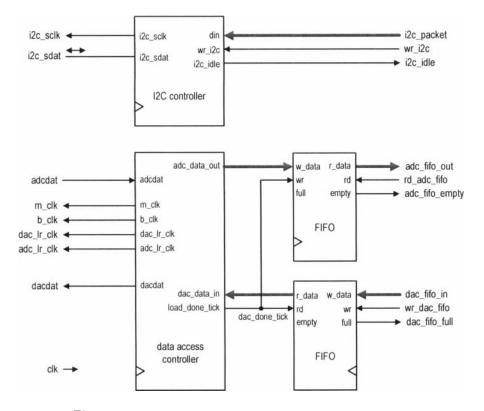

| 19.4    | Audio                | codec controller IP core development        | 572 |

|         | 19.4.1               | Complete audio codec controller             | 572 |

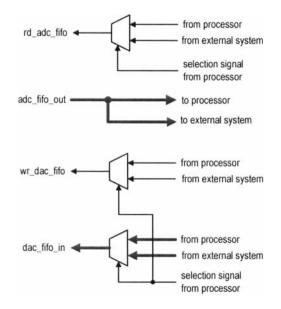

|         | 19.4.2               | Avalon interfaces                           | 574 |

|         | 19.4.3               | Register map                                | 575 |

|         | 19.4.4               | Wrapped audio codec controller              | 575 |

|         | 19.4.5               | SOPC component creation                     | 577 |

| 19.5    | Codec                | driver                                      | 577 |

|         | 19.5.1               | I <sup>2</sup> C command routines           | 577 |

|         | 19.5.2               | Data source select routine                  | 578 |

|         | 19.5.3               | Device initialization routine               | 578 |

|         | 19.5.4               | Audio data access routines                  | 579 |

| 19.6    | Testing              | g program                                   | 580 |

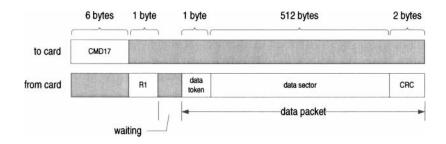

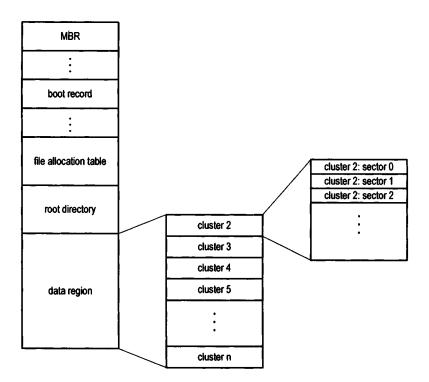

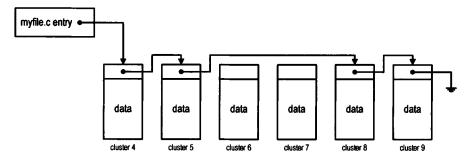

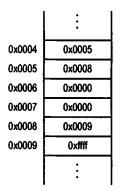

| 19.7    | Audio                | file processing                             | 583 |