Thanks to Beregnyei Balazs, who tried to dissect the NMOS 6502 at transistor level.

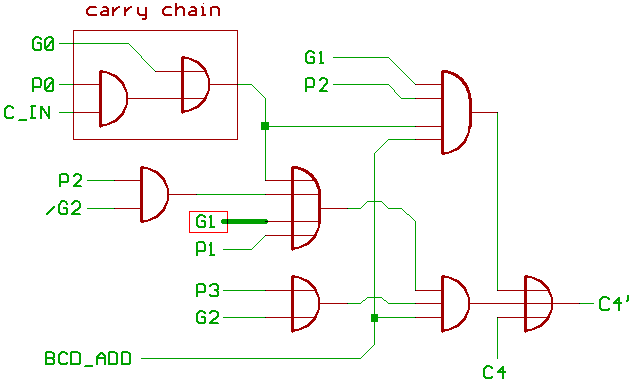

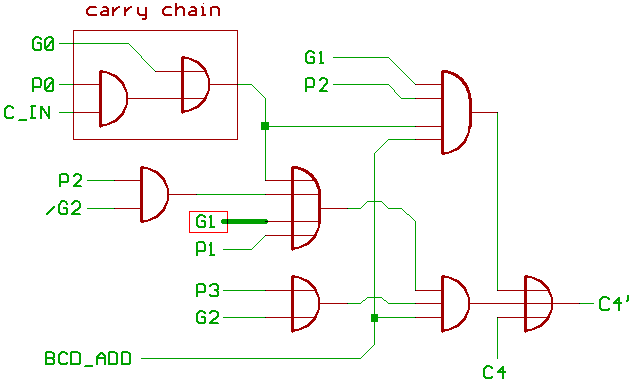

Tried to redraw the pseudo_tetrade detection at gate level.

Implementation is a little bit different inside the 6502,

because it makes use of NOR, NAND, XNOR gates.

The grey marked box could be a part of the carry chain,

because C1 is the output carry from ALU Bit 0.

(But in the NMOS 6502, it isn't.)

Note the red marked 4_input_OR gate.

If the ALU uses OR based propagate_signals (P1=A1|B1),

like in the 6502, the G1 input of this gate isn't necessary.

Wiring the carry_outputs together by using open_collector NANDs,

for building a faster/simpler variant:

Note: carry output is low_active.

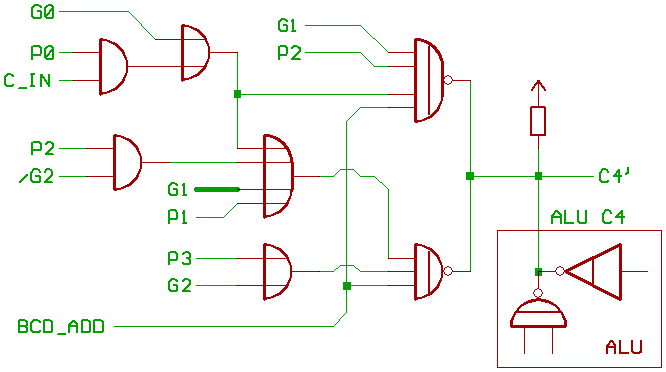

Basically, we are building up two carry chains:

One mostly for binary arithmetic, that detects results > (decimal) 15.

Note the logic gates in the green marked box, that are part of the

ALU carry chain.

And another one to be used in decimal mode only, that detects results from (decimal) 10..15.

[HOME] [UP]/ [BACK] [1] [2] [3] [4] [5] [6] [7] [NEXT]

(c) Dieter Mueller 2006