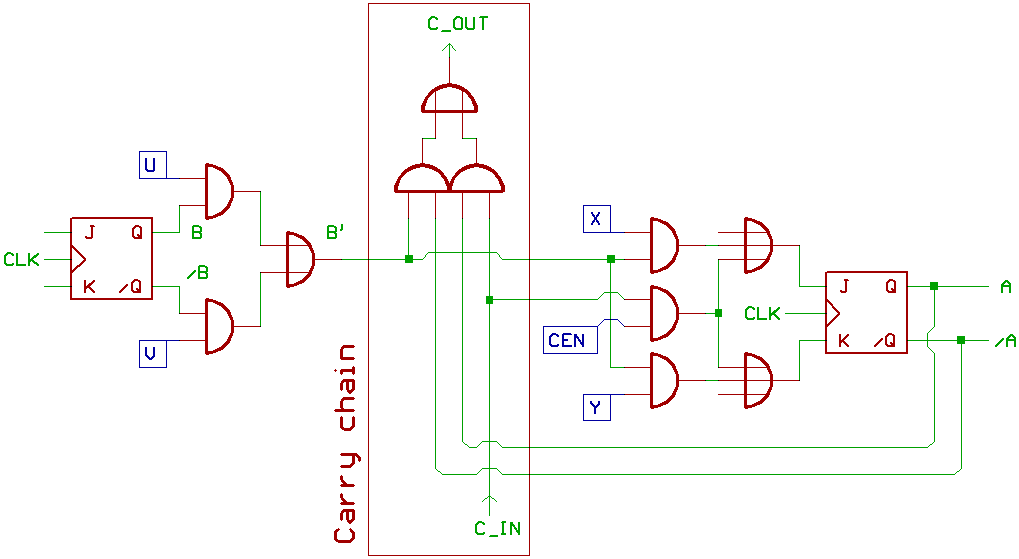

And now, the miracle happens:

And yes, all we really need is this AND/OR combination gate

for forming up the carry chain, plus one additional AND gate

fed by the carry input and the CEN control signal.

Downside is, that performing arithmetic operations takes

two clock cycles.

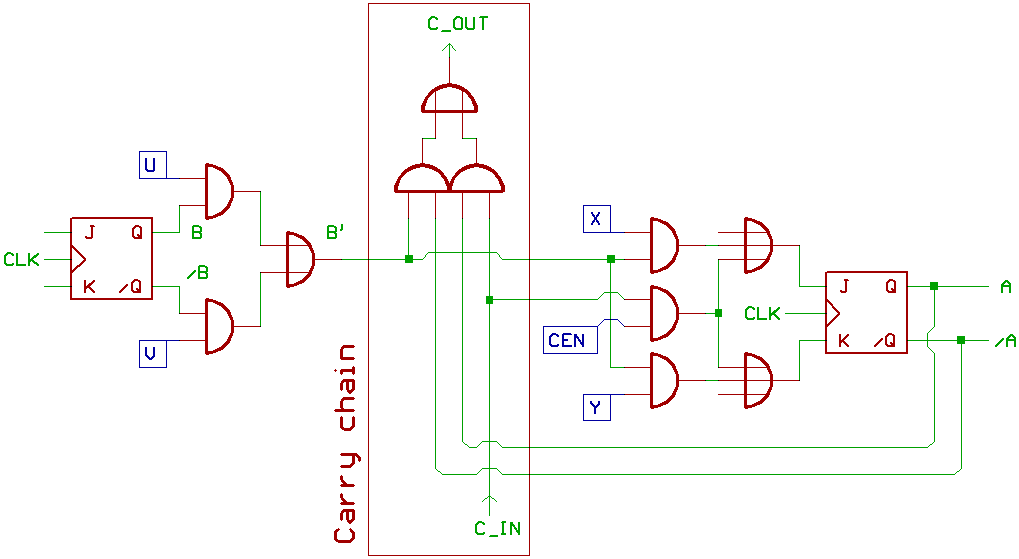

Now a close look to the carry chain:

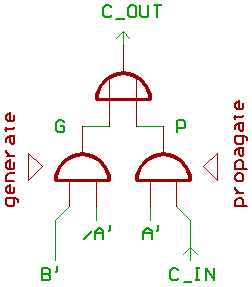

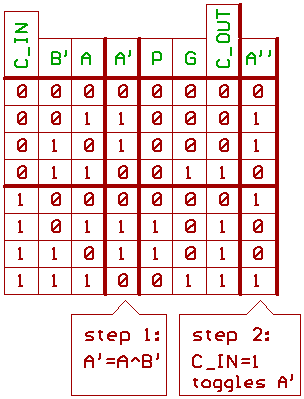

Don't get confused now.

A' means "contents of the A flipflop after the first clock pulse", A'' means "contents of the A flipflop after the second clock pulse".

Now to describe, how it works.

Example:

A=A+B //ADC, C_IN is high_active carry

Step 1: (first clock cycle)

U=1, V=0, X=1, Y=1, CEN=0: A'=A^B //XOR

After the first clock cycle, the carry ripples through

the carry chain according to B', A'.

Step 2: (second clock cycle)

U=1, V=0, X=0, Y=0, CEN=1: A''=A'^carry.

A=A-B: C_IN is low_active borrow

Step 1: U=0, V=1, X=1, Y=1, CEN=0: A'=A^/B

Step 2: U=0, V=1, X=0, Y=0, CEN=1: A''=A'^carry

A=A+1:

Only one step required. Set ALU carry input to 1.

Step 1: U=0, V=0, X=0, Y=0, CEN=1

A=A-1: A=A+(-1) set ALU carry input to 0

Step 1: U=1, V=1, X=1, Y=1, CEN=0: A'=A^(-1)

Step 2: U=1, V=1, X=0, Y=0, CEN=1: A''=A'^carry

A=-A: set ALU carry input to 1

Step 1: U=1, V=1, X=1, Y=1, CEN=0: A'=A^(-1)

Step 2: U=0, V=0, X=0, Y=0, CEN=1: A''=A'^carry

[HOME] [UP]/ [BACK] [1] [2] [3] [4] [5] [6] [7] [8] [NEXT]

(c) Dieter Mueller 2012