PLA4 controls load and output enable for all registers,

except for the flags.

(Clock gating)

Note:

+ means, no transistor.

O means, transistor (BC847 or BC857) at this location.

!S0-O++OO+O++O+O++++

S0-+O+++O++O+++OO++

!S1-++++O+++OOOOO+++

S1-+++O+++++++++O++

!S2-OO+O+OO++OO+OO++

S2-++O+O++OO++O++++

CMD7-++++O+++O++O++++

!CMD8-+++++++O+++O++++

CMD8-++++O+++++++++++

!CMD9-+++++++++++++O++

!CMD10-+++O++++++++++++

!CMD11-++++++++++++O+++

TRUE-++++++++++++O+++

!RES_F-++++++++++++O+++

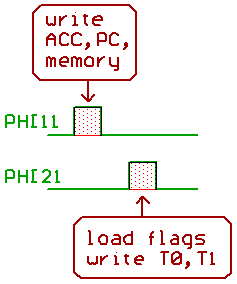

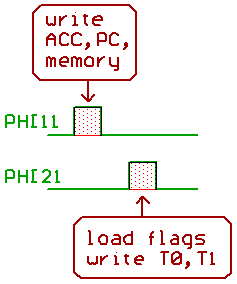

PHI21-+++++OOOOO++++++

PHI11-++++++++++OO++++

-++++++++++++++++

-++++++++++++++++

||||||||||||||||

O+++++++++++++++-OAT0

+OO+++++++++++++-OAT1

+++OO+++++++++++-ODT0

+++++O+OO+++++++-LT0

++++++O+++++++++-LT1

+++++++++O++++++-LIR

++++++++++O+++++-LPC

+++++++++++O++++-LACC

++++++++++++OO++-OACC

++++++++++++++++-

//looks like OAT1=!OAT0. OAT0 = !S2 & !S0 //address_bus=T0 in step 0, step 2 OAT1 = !S2 & S0 | S2 //address_bus=T1 in step 1,3,4,5 ODT0 = !S2 & S1 & !S0 & !CMD10 //data_bus=T0 in step 2 if CMD10=0 //T0->T1 ODT0 |= S2 & !S1 & !S0 & CMD8 & CMD7 //data_bus=T1 in step 4: memory write LT0 = PHI21 & !S2 & S0 //load T0 in step 1,3 LT0 |= PHI21 & S2 & !CMD8 //load T0 in step 4,5 if CMD8=0 LT0 |= PHI21 & S2 & !S1 & S0 & CMD7 //load T0 in step 5 if CMD7=1 LT1 = PHI21 & !S2 & !S0 //load T0 in step 0,2 LIR = PHI21 & !S2 & !S1 & !S0 //load instruction register in step 0 LPC = PHI11 & !S2 & !S1 //load PC in step 0,1 LACC = PHI11 & S2 & !S1 & !S0 & !CMD8 & CMD7 //load ACC in step 4 ? OACC = !S2 & !S1 & S0 & !CMD11 & TRUE & !RES_FLAG //step 1: ACC as index OACC |= !S2 & S1 & S0 & !CMD9 //step 3: read ACC for data calculation OPC = !OACC

To clarify things, a look to PHI11 and PHI21:

[HOME] [UP]/ [BACK] [1] [2] [2] [4] [5] [6] [7] [8] [NEXT]

(c) Dieter Mueller 2005